# 高電圧直流送配電向け電力変換器の 高効率化に関する研究

2020年2月

千葉大学大学院融合理工学府 基幹工学専攻電気電子工学コース 石橋 卓治

# (千葉大学審査学位論文)

# 高電圧直流送配電向け電力変換器の 高効率化に関する研究

2020年2月

千葉大学大学院融合理工学府 基幹工学専攻電気電子工学コース 石橋 卓治

# 目次

| 第1章 緒論                       | 1  |

|------------------------------|----|

| 1.1. 研究背景                    | 1  |

| 1.1.1. 再生可能エネルギーの導入動向        | 1  |

| 1.1.2. 洋上風力発電の動向             | 1  |

| 1.1.3. 再生可能エネルギー導入の経済的メリット   | 2  |

| 1.1.4. 再生可能エネルギー導入の課題        | 4  |

| 1.1.5. 洋上風力発電における課題          | 5  |

| 1.1.6. 次世代の電力系統              | 5  |

| 1.2. 研究目的                    | 7  |

| 1.3. 論文構成                    | 8  |

| 参考文献                         | 10 |

|                              |    |

| 第2章 高電圧直流送配電向け電力変換器          | 12 |

| 2.1. 技術背景                    | 12 |

| 2.1.1. 高圧直流送電                | 12 |

| 2.1.2. HVDC 送電と HVAC 送電の比較   | 13 |

| 2.1.3. HVDC 送電用電力変換器の方式      | 14 |

| 2.2. 適用を想定する電力系統の構成          | 15 |

| 2.2.1. HVDC 送電用自励式変換器        | 15 |

| 2.2.2. 洋上風力発電における直流化の動向      | 16 |

| 2.2.3. 適用を想定する電力系統の構成        | 19 |

| 2.4. 高圧 DC/DC 変換器の回路方式       | 21 |

| 2.4.1. FTF 方式の先行研究           | 21 |

| 2.4.2. DAB 方式の先行研究           | 23 |

| 2.4.3. その他の方式                | 26 |

| 2.5. まとめ                     | 28 |

| 参考文献                         | 29 |

| 第3章 高圧 DC/DC 変換器の回路構成と電圧制御法  | 32 |

| 3.1. 基本回路構成                  |    |

|                              |    |

| 3.1.2. 高圧 DC/DC 変換器の回路構成比較   |    |

| 3.1.3. 提案する高圧 DC/DC 変換器の回路構成 |    |

|                              |    |

| 3.2. 高圧 DC/DC 変換器の電圧制御法             | 36 |

|-------------------------------------|----|

| 3.2.1. 電圧バランス制御                     | 36 |

| 3.2.2. 補助変換器の必要容量                   | 38 |

| 3.2.3. 補助変換器の制御法                    | 39 |

| 3.3. 回路定数設計                         | 40 |

| 3.3.1. 変圧器漏れインダクタンスの設計              | 40 |

| 3.3.2. スナバキャパシタの設計                  | 40 |

| 3.4. シミュレーション検証                     | 41 |

| 3.4.1. セル動作のシミュレーション検証              | 41 |

| 3.4.2. 電圧バランス制御のシミュレーション回路          | 42 |

| 3.4.3. 電圧バランス制御のシミュレーション結果          | 44 |

| 3.5. 実験結果                           | 46 |

| 3.5.1. ユニット出力電圧バランス制御の確認            | 47 |

| 3.5.2. セル電圧バランス制御の確認                | 48 |

| 3.5.3. ユニット入力電圧バランス制御の確認            | 49 |

| 3.6. まとめ                            | 49 |

| 参考文献                                | 50 |

|                                     |    |

| 第4章 高圧 DC/DC 変換器用変圧器の小型高効率化に向けた検討   | 51 |

| 4.1. 2 直列 3 並列接続した半導体素子の適用          | 51 |

| 4.1.1. 半導体素子の直列接続に関する先行研究と課題        | 51 |

| 4.1.2. 半導体素子の並列接続に関する先行研究と課題        | 54 |

| 4.1.3. 本学位論文で提案する2直列3並列接続半導体素子の実現方法 | 56 |

| 4.2. ZVS 動作を利用した半導体素子の直列接続          | 56 |

| 4.3. スナバキャパシタ容量の設計                  | 57 |

| 4.3.1. ZVS 動作による容量の制限               | 57 |

| 4.3.2. 電圧アンバランスによる容量の制限             | 58 |

| 4.3.3. スナバキャパシタの容量設計                | 59 |

| 4.3.4. シミュレーション結果                   | 61 |

| 4.4. スイッチング試験                       | 63 |

| 4.4.1. 接続導体設計                       | 63 |

| 4.4.2. スイッチング試験                     | 64 |

| 4.5. 変圧器の鉄心構造                       | 69 |

| 4.6. 回路方式による変換効率と半導体素子数および変圧器重量の比較  | 69 |

| 4.7. まとめ                            | 70 |

| 参考文献                                | 71 |

| 第5章 セル故障時における継続運転を実現するための電圧設定方法  | 73  |

|----------------------------------|-----|

| 5.1. DAB コンバータにおける課題             | 73  |

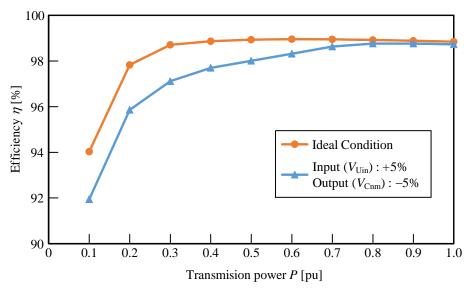

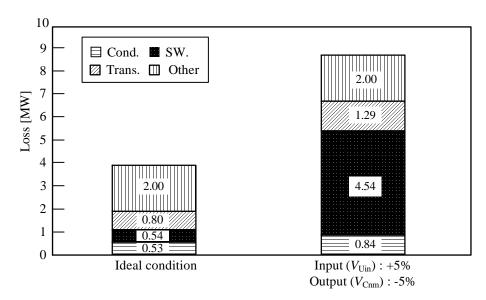

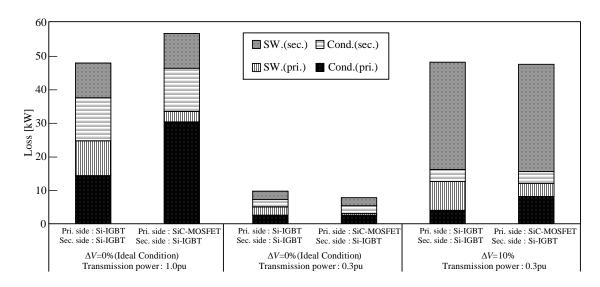

| 5.2. 直流電圧変動の影響                   | 74  |

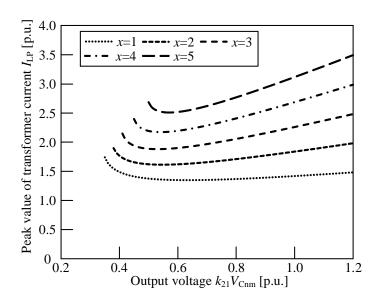

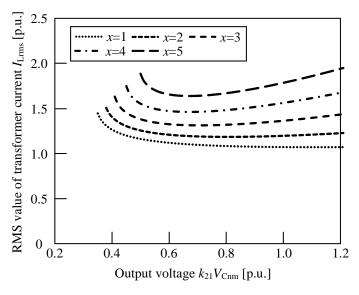

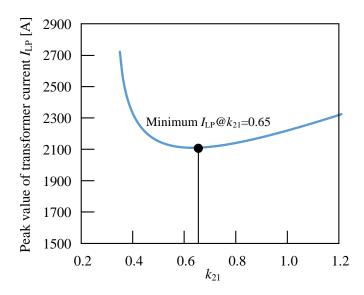

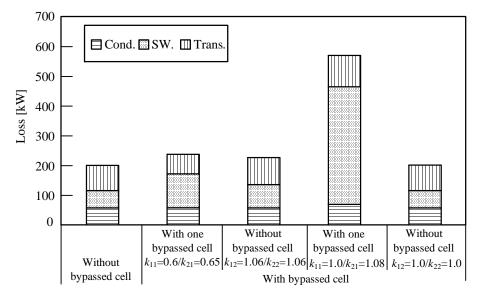

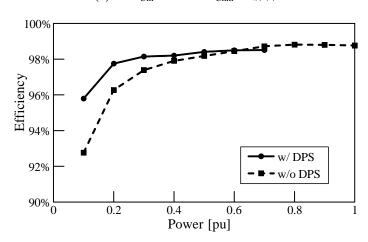

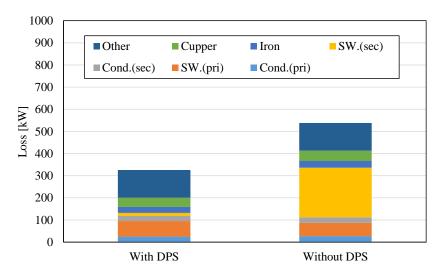

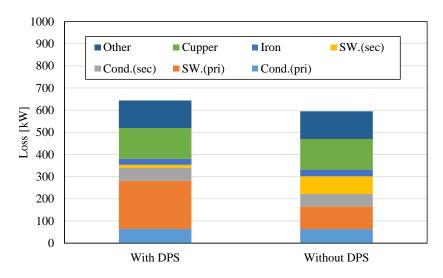

| 5.2.1. 変換効率試算結果                  | 74  |

| 5.2.2. 半導体損失の算出方法                | 77  |

| 5.2.3. SiC-MOSFET の適用検討          | 77  |

| 5.3. セル故障発生時の運転継続                | 79  |

| 5.3.1. セル故障数の影響                  | 79  |

| 5.3.2. セル出力電圧の設定方法               | 82  |

| 5.4. まとめ                         | 85  |

| 参考文献                             | 86  |

|                                  |     |

| 第 6 章 Dual-Phase-Shift 制御の適用検討   | 87  |

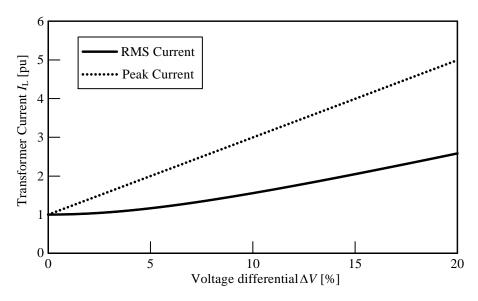

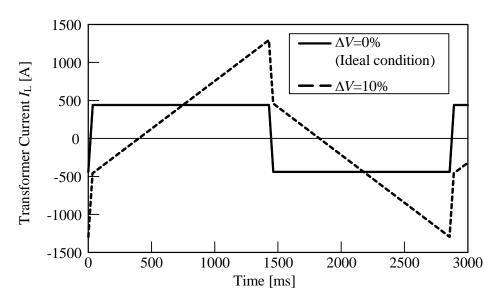

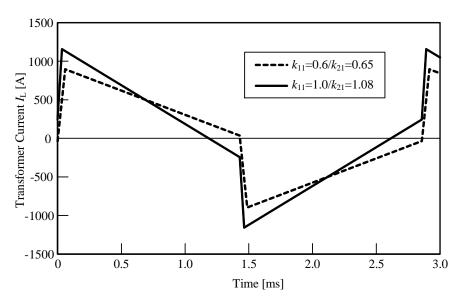

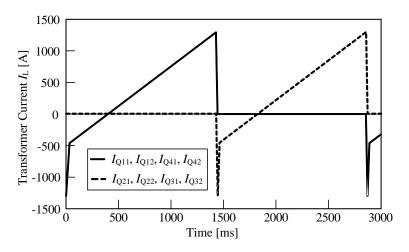

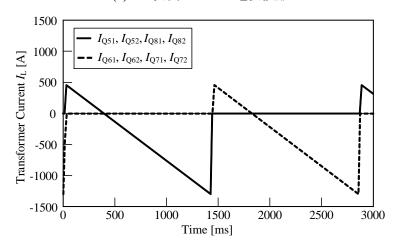

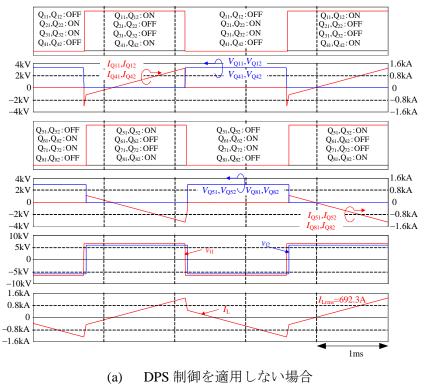

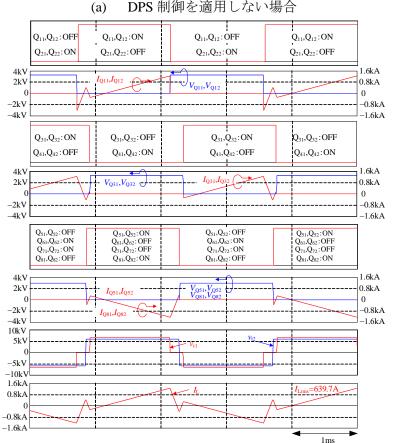

| 6.1. 電圧変動発生時における各半導体素子の電流波形      | 87  |

| 6.2. 電圧変動発生時における損失増加抑制方法         | 87  |

| 6.2.1. 電圧変動時に巻き数比やインダクタンスを追加する方式 | 88  |

| 6.2.2. 半導体素子のスイッチングパターンを制御する方式   | 89  |

| 6.2.3. 出力する交流電圧をマルチレベル化する方式      | 89  |

| 6.2.4. 高圧 DC/DC 変換器に適用する方式       | 91  |

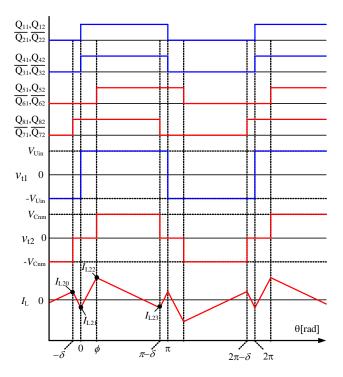

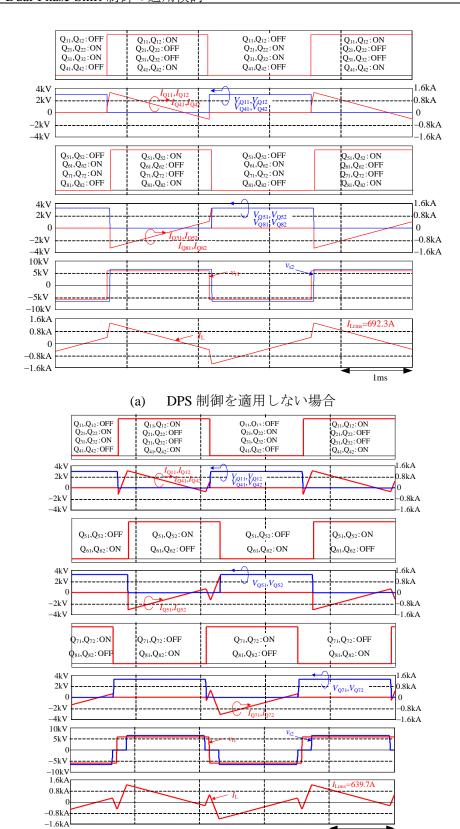

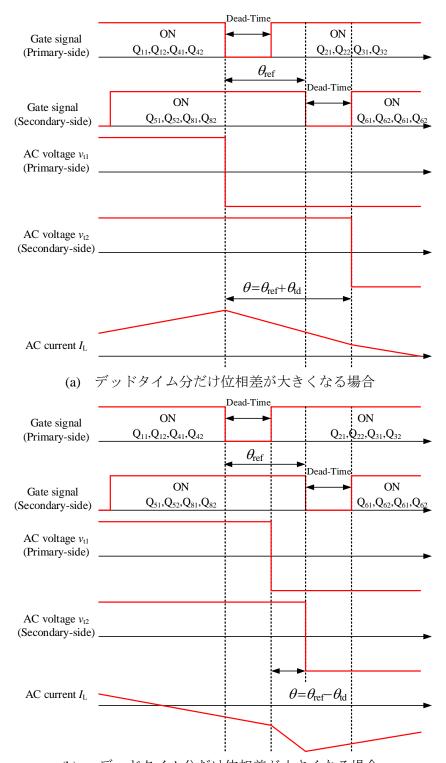

| 6.3. Dual−Phase−Shift 制御の適用検討    | 92  |

| 6.3.1. 1 次側適用時の送電電力制御            | 92  |

| 6.3.2. 2 次側適用時の送電電力制御            | 93  |

| 6.3.3. 各位相差の設定方法                 | 95  |

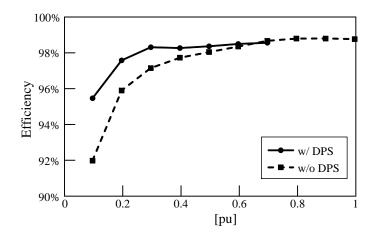

| 6.4. 適用効果の検証                     | 96  |

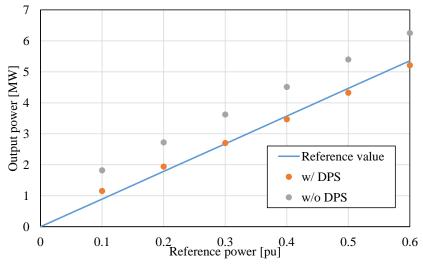

| 6.4.1. シミュレーション結果                | 96  |

| 6.4.2. 変換効率の試算結果                 | 99  |

| 6.4.3. デッドタイムによる送電電力誤差           | 101 |

| 6.5. まとめ                         | 103 |

| 参考文献                             | 104 |

|                                  |     |

| 第7章 結論                           | 105 |

| 7.1. 本研究の成果                      | 105 |

| 7.2. 今後の課題と展望                    | 107 |

| 7.2.1. 今後の課題                     | 107 |

| 7.2.2. 今後の展望                     | 108 |

| <b>参考文献</b>                      | 100 |

| \/ <b>L</b> |

|-------------|

| 1/1/        |

|             |

| 発表論文等 | 110 |

|-------|-----|

| 謝辞    | 111 |

# 第1章

# 緒論

### 1.1. 研究背景

#### 1.1.1. 再生可能エネルギーの導入動向

地球温暖化対策の一環として、太陽光や風力に代表される再生可能エネルギーを利用し た発電が盛んに取り組まれている。さらに、2011年3月11日に発生した震災に端を発した 脱原発化の流れもあり,原子力に代わるエネルギー源として再生可能エネルギー資源の積 極的な活用が以前にも増して求められるようになっている。再生可能エネルギー資源の中 において突出した資源量を誇るものが洋上風力であり、将来的に大規模な導入が見込まれ ている。欧州では、2020年に全電力発電量の20%を再生可能エネルギーにするという目標 がある。この目標を達成すべく欧州各国は独自に目標値を定め,再生可能エネルギー導入の 促進政策(再生可能エネルギー固定価格買い取り制度: FIT, Feed in Tariff)を進めている。その 流れの中でドイツは、2022 年までに原発を停止し再生可能エネルギーへシフトするエネル ギー転換政策をとった。2020年には、風力発電による発電量を最終エネルギー消費量の35% とすることを目標として掲げており、洋上風力 10GW の導入見通しを示した。さらに、イ ギリスやデンマーク・スペインでも積極的な導入を目指した動きがある<sup>(1)~(3)</sup>。同様に日本政 府は、第5次エネルギー基本計画の中で、2030年のエネルギーミックス実現と2050年への シナリオ設計を検討するにあたり、脱炭素化やエネルギー自給率向上を目的とした再生可 能エネルギーの主力電源化を検討しており、2030年度には全電力発電量の22~24%を再生 可能エネルギーにするための政策的な誘導を積極的に行うことを定めた(4)。

#### 1.1.2. 洋上風力発電の動向

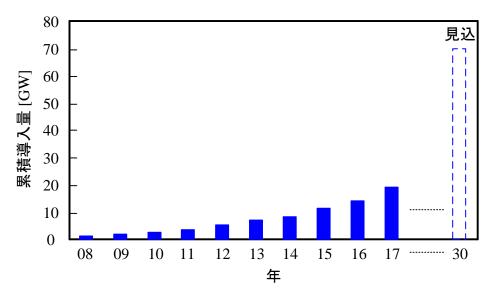

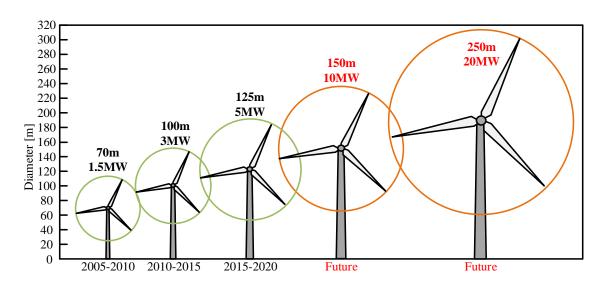

再生可能エネルギーは、各国政府の政策的な支援のもとに継続的な導入が進められると考えられる。洋上風力発電に関しては、特に欧州で積極的に導入が進んでおり、図 1.1 に示すように継続的な増加が予想され 2017 年末時点で 19GW から 2030 年には 70GW を超えると見込まれている(5)。また、図 1.2 に示すように風力発電機を大型化することで発電機単機の出力を増加させることで発電コスト低減の要求に対応する動きがあり、近い将来、風車の出力は 10MW まで向上し、さらにその先には、ブレードの直径が 250m となり、1 機当たりの発電電力は 20MW にまで及ぶと想定されている(6,0)。

図 1.1 洋上風力発電の累積導入量の推移(5)

図 1.2 風力発電機大型化の動向(6),(7)

# 1.1.3. 再生可能エネルギー導入の経済的メリット

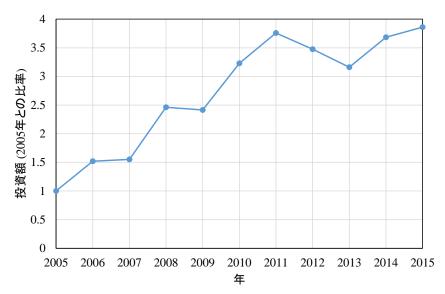

再生可能エネルギーの積極的な導入は、地球温暖化対策の一環でもあるが、同時に新たな投資と雇用を創出し、経済的な成長をもたらすという側面もある(8)~(10)。特に大規模な再生可能エネルギーの導入には、建設・輸送や工場での生産、生産に必要な電力の発電・電気設備・水道設備などの間接的な波及効果も大きくなる。図 1.3 に世界の再生可能エネルギーへの関連投資の推移を示す。2013 年に一時期投資が落ち込んでいる時期があるが、2005 年を基に比較すると 4 倍近くまで投資額が増加していることが確認できる。また、日本に限定すると、2030 年に第 5 次エネルギー基本計画に定められた見通しをすべて達成した場合の見込みとして、必要な総投資額が 28 兆円、最終的な経済波及効果は 55.4 兆円との試算結果も

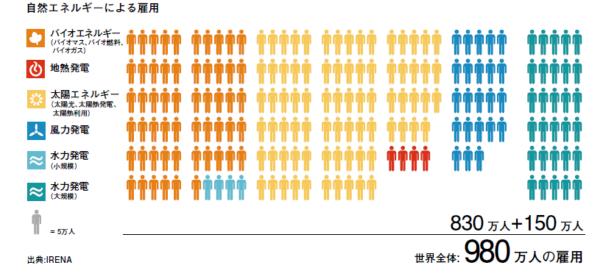

ある<sup>(9)</sup>。さらに、2015年の段階で世界では、再生可能エネルギー関連事業で830万人が雇用されていたが、図1.4に示すように2016年の時点での雇用者数が980万人と1年間で新たに150万人の雇用を創出した<sup>(11)</sup>。このように、再生可能エネルギーは地球温暖化対策としてだけではなく、利益と雇用を生み出す大きな成長産業として今後の社会を支えるものとなることは明らかである。

図 1.3 世界の再生可能エネルギーへの関連投資額の推移(2005 年基準) (REN21 「Renewables 2016 Global Status Report」(11)を基に作成)

図 1.4 世界の再生可能エネルギー関連雇用者数(2016 年) (出典: REN21 「Renewables 2016 Global Status Report」 (11))

#### 1.1.4. 再生可能エネルギー導入の課題

再生可能エネルギーの導入は新たな投資を呼び込み、利益と雇用を創出するが、一方で導入量を増加させるにあたってはいくつかの課題も存在する。特に大きな課題としてあげられるものとしては、大規模な再生可能エネルギーを導入した場合に周囲の環境へ与える影響を事前に事業者が評価する環境アセスメントに必要な手続きが長期化することや、接続する電力系統の設備容量が不足していることなどである。環境アセスメントについては、政策的な課題であり、関係省庁が手続きの簡素化・期間短縮に向けて動き始めている。

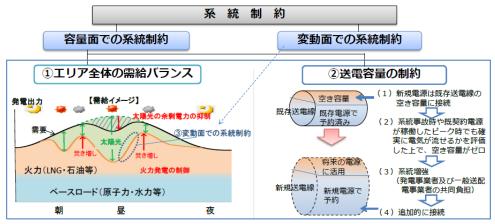

系統容量については, 予備率の考え方など一部政策的な要因も含まれるが, 根本的には技 術的な課題となる。図 1.5 に日本における系統制約の分類について示す。日本の電力系統の 構成としては、電力会社が所有する大規模な電源(火力発電など)と需要地を結ぶ形で形成さ れている。一方で,再生可能エネルギーの中でも主たる電源として期待されている太陽光や 風力発電などは,大規模になるほど,広大な敷地が必要となることや,日射量・風況のため 需要地から離れた場所で発電されることが多いため、既存の電力系統が持つ容量と再生可 能エネルギーによる電源の立地が必ずしも一致していない。また,電力の需要と供給のバラ ンスは一致させる必要があるが, 再生可能エネルギーの発電電力は日射量・風況などの自然 環境に依存して大きく変動するため,変動分を補うだけの調整力が必要となる。また,既存 の電力系統の送電容量は電力会社が所有する大規模な電源の容量を基に設計されており、 新たに大規模な電源を接続すると電力系統の送電容量が不足することになることから、送 電設備の新設による増強が必要であり、膨大な額の投資となる。世界でも同様の問題として、 送電容量を増強するための送電鉄塔を新設することが困難であるという状況が起こってい る。特にドイツでは、北海の洋上風力で発電した電力を需要地の内陸部へ送電する必要があ るが, 新たに敷設する必要がある 3600km の送電線のうち, 2012 年時点で 90km しか建設が 進んでいない(12),(13)。

図 1.5 日本における系統制約の分類

(出典:資源エネルギー庁:「再生可能エネルギーの大量導入時代における 政策課題と次世代電力ネットワークの在り方」  $^{(12)}$ )

以上から,再生可能エネルギー導入には①電力系統の需給バランス,②電力系統の送電容量,③出力が変動することによる調整力が課題となる。

#### 1.1.5. 洋上風力発電における課題

前節では、再生可能エネルギーによる発電電力を電力系統に連系する際の課題について整理を行った。一方で、再生可能エネルギーとして莫大な資源量を誇る洋上風力発電においては、発電してから電力系統に連系するまでの発電システムにも課題が存在する。前述の通り洋上風力発電では、発電コスト低減の要求に対して、風力発電機の単機の容量増加がトレンドとなっている<sup>(の,(7)</sup>。しかし、風力発電機が大型化することに伴って、風車のブレードも大型化するので、隣接する風車との距離を従来よりも長く確保する必要がある。また、発電機の出力電力が増加することで、陸上までの発電電力を送電する洋上の電力系統で発生する損失が大きくなるという懸念がある。このような背景から、洋上の電力系統では、送電時の電圧を高圧化したり、さらに洋上変換所にて高電圧直流に変換した後に陸上に送電が行われている<sup>(14)-(17)</sup>。

また、研究レベルでは、風力発電機の出力を交流ではなく数十 kV の直流に変換した後に 洋上の電力系統に連系することも検討されている(18)~(21)。

#### 1.1.6. 次世代の電力系統

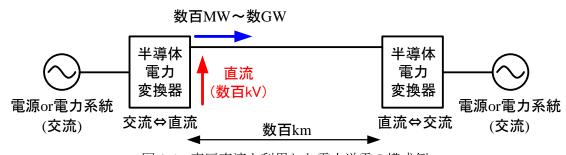

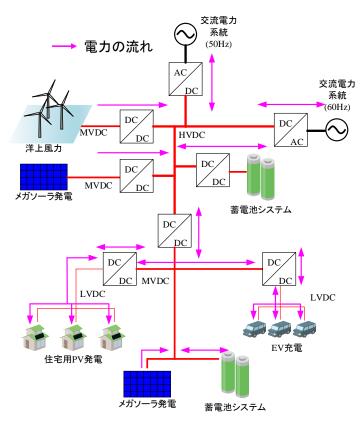

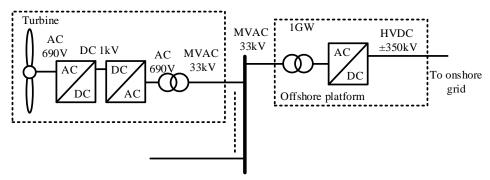

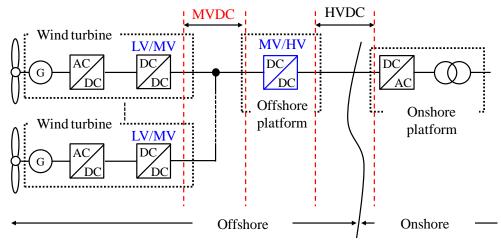

上記のような課題を克服する技術として、高圧直流(HVDC)送電が検討されており、欧州では先行して導入が進められている。図 1.6 に HVDC 送電を使用した電力系統の構成を示す。HVDC 送電は半導体電力変換器によって数百 kV の交流から数百 kV に変換(整流)された直流によって送電を行う技術であり、送電線で表皮効果が発生しない点や、インピーダンスによる位相ずれを調節する調相設備が不要になるため、送電が長距離化するほど効率面、コスト面でメリットが大きくなる。既に送電設備用の用地に制約があるケースや、洋上風力などの長距離にわたる送電を行うケースや周波数が異なる電力系統間の連携において実用化されており、今後さらに増加するものと考えられる(22)。

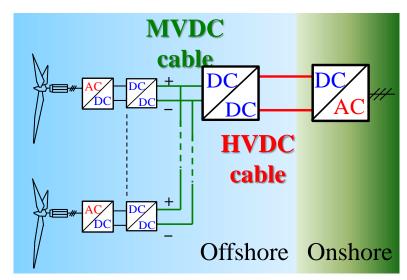

図 1.6 高圧直流を利用した電力送電の構成例

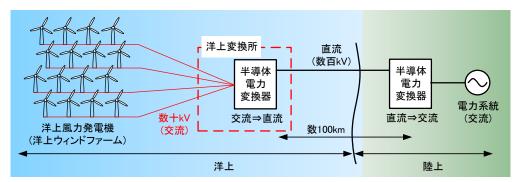

図 1.7 高圧直流を利用した洋上風力発電における電力系統の構成例

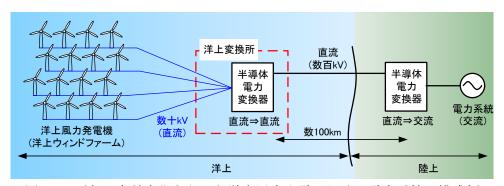

図 1.8 更なる高効率化を狙った洋上風力発電における電力系統の構成例

これまでに述べたように洋上風力発電にも HVDC 送電の導入が進んでおり、電力系統の構成としては図 1.7 に示すようになる。一方で、図 1.8 に示すような、さらなる高効率化を目的として、前節で説明したような洋上風力発電の交流出力を数十 kV の直流(MVDC)に変換した後に、洋上変換所にて数百 kV の HVDC に変換して陸上へ送電する構成も考えられる。

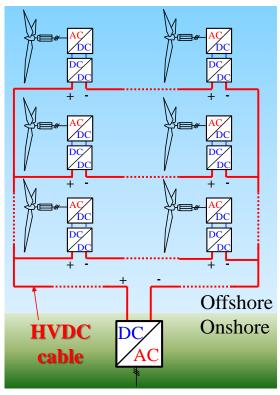

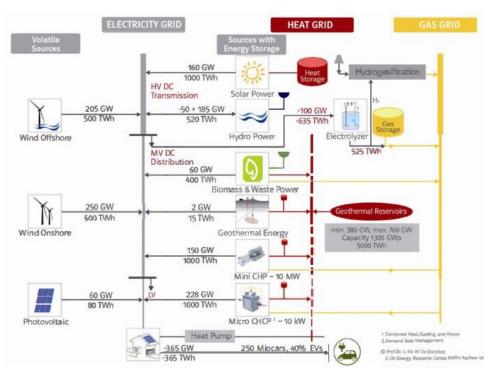

今後より一層の再生可能エネルギーの導入と有効利用を考えた場合に、図 1.9 に示すような HVDC や MVDC または数 kV 程度の直流(LVDC)を利用した電力系統が増えてくるものと想定される。図 1.9 の電力系統では、洋上風力発電に限らず大規模太陽光発電(メガソーラ)や蓄電池システムのほかに、異なる周波数の交流系統も AC/DC 変換器(半導体電力変換器)を介して HVDC に連系されている。洋上風力やメガソーラで発電された電力は、MVDC から DC/DC 変換器で HVDC に変換した後に送電され、そのぞれの交流系統内や住宅、EVの充電に使用される。さらに、余剰電力は MVDC で蓄電池に蓄えられ、電力需要が増加した場合には、DC/DC 変換器で HVDC に変換した後に送電する。また、住宅用 PV 発電や EV 充電システム、中規模のメガソーラや蓄電池システムが、LVDC や MVDC で連系されることで、住宅用 PV 発電の余剰電力やメガソーラで発電された電力が他の住宅や EV の充電に使用される。

図 1.9 直流が適用された次世代の電力系統の構成例

# 1.2. 研究目的

本研究の最終目的は、上記のような背景から導入が想定される図 1.9 に示す電力系統に適 用する DC/DC 電力変換器の中で、MVDC と HVDC の間で電力変換を行う高電圧大容量 DC/DC 変換器(以下、高圧 DC/DC 変換器)を実現することである。この DC/DC 変換器は、 異なる電圧レベルの直流に変換することが要求されることから安全面と構成する部品の対 地絶縁等の観点から絶縁型の変換器であることが望まれる。また, 再生可能エネルギーの導 入をさらに促進するためのものであるため, 高効率な電力変換が必須となる。これらの要求 を満たす回路方式として現在の HVDC 送電に適用されている MMC 型変換器を使用する構 成(FTF 方式)が有力となるが,動作特性上半導体素子がハードスイッチングとなり,損失が 大きくなるため高効率な電力変換器の実現には課題となる。そこで、絶縁型 DC/DC 変換器 である DAB(Dual-Active Bridge)コンバータをセルとしてこれを多数直並列接続する方式 (DAB 方式)が考えられる。DAB コンバータは特徴として ZVS(Zero-Voltage Switching)動作が 実現できるため高効率化には有利な方式である。 しかし,DAB コンバータで高圧 DC/DC 変 換器を構成すると、半導体素子耐圧の制約を受けて DAB コンバータの必要数が増加し、こ れに伴って必要な変圧器数も増加することからシステムの大型化が懸念される。高圧 DC/DC 変換器の回路構成としては、上記のような長所と課題を踏まえて決定する必要があ る。

本論文では、高効率な高圧 DC/DC 変換器の実現に向けて、DAB 方式を基にした新たな回路方式の提案や電圧制御方式の提案を行う。さらに、高圧 DC/DC 変換器に関する様々な現象に対する解析などを詳細に行うことで課題を明らかにし、その解決法の提案を行う。特に、以下の事項について、明確な指針を得ることを目的とし、数十kV の直流と数百kV の直流の間で高効率な電力変換を実現する高圧 DC/DC 変換器の基本的な設計指針を明らかにする。

- ・高圧 DC/DC 変換器の回路方式と電圧制御法

- ・高圧 DC/DC 変換器用変圧器の小型化

- ・セル故障時における継続運転を実現するための電圧設定方法

- ・実用性の高い電圧変動発生時における高効率化の手法

以上により、高圧 DC/DC 変換器の実現可能性や有用性を検証し、次世代の電力系統を実現するうえで必要となる電力変換器に関する基盤技術を確立する。

#### 1.3. 論文構成

本論文は、以下の全7章から構成される。

#### 第1章 緒論

本論文の背景、課題、目的を明らかにし、本研究の位置づけを示す。

#### 第2章 高電圧直流送配電向け電力変換器

現在の高圧直流送電の概要と優勢を明らかにし、適用される各回路方式の特徴を整理する。本研究で提案する高圧 DC/DC 変換器の適用先である電力系統を明らかにするとともに高圧 DC/DC 変換器の電気的仕様を整理する。さらに、先行研究を例に具体例を示しながら各回路方式の特徴・長所・課題を整理し、高圧 DC/DC 変換器の回路方式の方向性を明らかにする。

#### 第3章 高圧 DC/DC 変換器の基本構成と電圧制御法

本論文で提案する高圧 DC/DC 変換器の基本的な回路構成を明らかにし、これを実現する ために必要な電圧制御法について検討を行う。また、シミュレーション解析を行うことで提 案する電圧制御法の有効性を明らかにする。

#### 第4章 高圧 DC/DC 変換器用変圧器の小型高効率化に向けた検討

本論文で提案する高圧 DC/DC 変換器は多数の DAB コンバータから構成されるため, DAB コンバータと同数の変圧器が必要となりシステムが大型化するという課題がある。そこで, 2 直列接続した半導体素子を適用することで必要セル数の削減を行う。また, 電力変換器の

高効率化の一手法として知られている半導体素子の並列接続についても検討を行う。これらについて先行研究を具体例に各種方式の課題を整理しつつ、本論文では新たな手法を提案し、シミュレーションおよび実験によりその有用性を明らかにする。

#### 第5章 セル故障時における継続運転を実現するための電圧設定方法

高圧 DC/DC 変換器は電力系統に適用するものであり、例えば半導体素子の故障などのために出力不可能となったセルが発生した場合においても送電動作を継続することが要求される。しかし、DAB コンバータでは、直流電圧が変動し変圧器の巻き数比の関係が崩れてしまい損失が悪化するという課題がある。そこで、まず直流電圧の変動が変換効率に及ぼす影響を明らかにする。その後、継続運転時において特定のセルでの損失の集中を抑制するための電圧設定方法を明らかにする。

#### 第6章 Dual-Phase-Shift 制御の適用検討

電圧変動発生時おいて損失を抑制する方式として知られている Dual-Phase-Shift 制御の適用を検討する。Dual-Phase-Shift は実現にあたり非常に複雑な式展開を必要としており、実用性が低いという課題がある。そこで、本論文で、より実現性を高めるべく簡易な計算により実現する方式を検討する。また、本論文で検討した方式により Dual-Phase-Shift 制御を適用した場合の効果について明らかにする。

#### 第7章 結論

本論文における成果をまとめ、今後の課題および展望について述べる。

# 参考文献

- (1) 佐野憲一郎, 高崎昌洋:「洋上風力発電用の高圧直流送電への適用を想定した複数の変換器モジュールによる直流昇圧方式の提案」,電力中央研究所 研究報告書 R12013 (2014)

- (2) 友永隆浩:「岐路に立つEUエネルギー政策」,三井物産戦略研究所レポート(2014)

- (3) 新エネルギー・産業技術総合開発機構:「再生可能エネルギー普及拡大にむけて克服すべき課題と処方箋」, NEDO 再生可能エネルギー技術白書第2版 (2014)

- (4) 経済産業省 資源エネルギー庁:「第5次エネルギー基本計画」(2018)

- (5) 株式会社三井住友銀行:「欧州洋上風力発電の現況」, (2018)

- (6) European Wind Energy Association: "The Economics of Wind Energy" (2009)

- (7) F. Blaabjerg and K. Ma, "Future on power electronics for wind turbine systems," IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol. 1, Issue 3 (2013)

- (8) 経済産業省 資源エネルギー庁: 「平成 28 年度エネルギーに関する年次報告(エネルギー白書 2017)」, 第2部エネルギー動向, (2017)

- (9) みずほ情報総研:「再生可能エネルギーの現状と将来-再生可能エネルギーの導入による 経済分析の視点から-」,みずほ情報総研レポート Vol.15 (2018)

- (10) 一般社団法人 日本風力発電協会(JWPA):「洋上風力発電の導入促進に向けて〜特に洋上風力新法に係る課題と要望〜」(2018)

- (11) Renewable Energy Policy Network for the 21st Century: "RENEWABLES 2016 GLOBAL STATUS REPORT" (2017)

- (12) 経済産業省 資源エネルギー庁:「再生可能エネルギーの大量導入時代における 政策 課題と次世代電力ネットワークの在り方」(2017)

- (13) 国際環境経済研究所 HP: http://ieei.or.jp/2012/12/expl121204/ (2014)

- (14) 石原孟: 「我が国における洋上風力発電実証研究の現状と将来展望」, 環境管理, Vol. 48, pp.779-785 (2012)

- (15) C. Meyer, M. Höing, A. Peterson, and R. W. De Doncker: "Control and Design of DC-Grids for Offshore Wind Farms", *IEEE Tans. on IA*, Vol.43, No.6, pp.1475-1482 (2007)

- (16) F. Deng, and Z. Chen: "An Offshore Wind Farm with DC Grid Connection an Its Performance under Power Systems Transients", Proc. of IEEE Power and Energy Society General Meeting, pp.1-8, Michigan, USA (2011)

- (18) J. Robinson, D. Jovcic, and G. Joós: "Analysis and Design of an Offshore Wind Farm Using a MV DC Grid", *IEEE Trans. on Power Delivery*, Vol.25, No. 4, pp.2164-2173 (2010)

- (19) C. Meyer, M. Hoing, A. Peterson, and R. W. De Doncker: "Control and Design of DC Grids for

- Offshore Wind Farms", IEEE Trans. on Industry Applications, Vol.43, No. 6, pp.1475-1482 (2007)

- (20) M. T. Daniel, H. S. Krishnamoorthy, and P. N. Enjeti: "A New Wind Turbine Interface to MVdc Collection Grid With High-Frequency Isolation and Input Current Shaping", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol.3, No.4, pp.967-976 (2015)

- (21) T. Jimichi, M. Kaymak, and R. W. De Doncker: "Design and loss analysis of a medium-voltage DC-DC converter intended for offshore wind farms", 2016 IEEE International Conference on Renewable Energy Research and Applications (ICRERA), pp.137-142 (2016)

- (22) Siemens: "High Voltage Direct Current Transmission -Proven technology power exchange-" (2011)

# 第2章

# 高電圧直流送配電向け電力変換器

本章では、本研究で対象とする高圧直流送電(以下、HVDC 送電)について概要を説明し、優位性と高圧直流送電に適用される半導体電力変換器の方式に関して開設する。さらに、次世代の電力系統に関する研究動向を紹介し、本研究で検討する高圧 DC/DC 変換器の位置づけを明らかにする。

#### 2.1. 技術背景

#### 2.1.1. 高圧直流送電

再生可能エネルギーの大量導入による系統制約を解決する技術として高圧直流(HVDC) 送電に注目が集まっている。HVDC 送電は主に大容量である長距離での送電に適用されている技術であり、欧州や中国で導入が進んでいる(1)。

図 2.1 に直流の分類イメージを示す。一般的にデータセンタ向けの直流 380V での給電も HVDC と呼称されているが、本研究で対象としている HVDC 送電とは、図 2.1 に示すよう な数百 kV の直流を使った送電である。HVDC 送電は、1954 年に ABB 社が世界で初めて実用化し、その後、様々な開発が続けられており、主に長距離での送電や国家間の電力系統の連携などに適用されている(2)~(6)。HVDC 送電では、第 1 章でも述べたように半導体電力変換器によって交流を直流に変換し後に、再度半導体電力変換器によって交流に変換されるため、交流回路と直流回路を分離でき、周波数の異なる電力系統間の連系や系統安定度の問題がないことが利点となり特に再生可能エネルギーの導入促進に有効な技術である。

図 2.1 直流の分類イメージ(1)

(出典:国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO):「直流送電技術 における NEDO の取組」(2019))

#### 2.1.2. HVDC 送電と HVAC 送電の比較

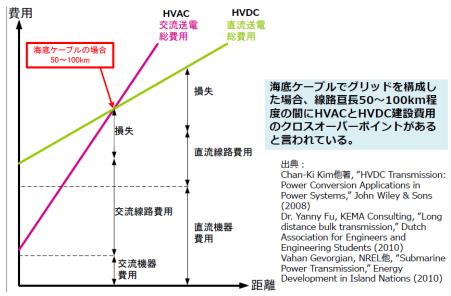

表 2.1 に HVDC 送電と HVAC(高圧交流)送電の比較を示す。HVDC 送電は,直流による電力送電であるため表皮効果がなくすべて有効電力となることから,交流とは異なり,無効電力の影響を受けない。さらに,HVAC 送電では 3 相分の導体が必要となるが,HVDC は送電線と帰線の 2 本分で良いため必要な導体のコストも抑えることが可能となる。また,HVAC 送電では,送電線に存在する寄生インピーダンスによる位相の遅れや進みのため送電容量が制限される。さらに他の電力系統と連系する場合には,連系先の電力系統と位相を一致させる必要がある。このように,HVDC 送電は HVAC 送電と比較してメリットが大きいが,電力変換器が必須となり,これがコストアップ要因となる。図 2.2 に送電距離による HVDC 送電と HVAC 送電のコスト比較を示す(8)。HVDC 送電は電力変換器のコストが高いため送電距離が短い場合には HVAC 送電より高コストになる傾向にある。しかし,送電距離が長くなると HVAC 送電の損失が増加することに伴って,コストが上昇するため HVDC 送電とコストが逆転するポイントが発生する。このポイントは一般的に架空送電線の場合 500~800km であり洋上風力発電のように海底ケーブルを使用する場合は 50~100km とされている(ワハ.6)。上記の通り,HVDC 送電は、長距離でかつ大容量の送電であるほどメリットがある。

表 2.1 HVDC 送電と HVAC 送電の比較(2)~(5)

| 項目        | HVDC 送電 | HVAC 送電         |

|-----------|---------|-----------------|

| 表皮効果による損失 | 無       | 有               |

| 導体コスト     | 小       | HVDC 送電より大      |

|           |         | 3 相分が必要であり、表皮効果 |

|           |         | と無効電力の影響を受けるため  |

| 鉄塔用用地     | 小       | HVDC 送電より大      |

|           |         | 導体3本分のスペースが必要   |

| 送電容量      | 大       | HVDC 送電より小      |

|           |         | ・表皮効果と無効電力の影響を  |

|           |         | 受け電流が制限される      |

|           |         | ・送電線の寄生インピーダンス  |

|           |         | (L,C)の影響を受ける    |

| 他の電力系統との連 | 低       | HVDC 送電より高      |

| 系の困難さ     |         | 連系する系統と位相を一致させ  |

|           |         | る必要がある          |

図 2.1 送電距離による HVDC 送電と HVAC 送電のコスト比較(8)

(出典:国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO):「次世代洋上直流送電システム開発事業」, スマートコミュニティ部成果報告会資料 (2016))

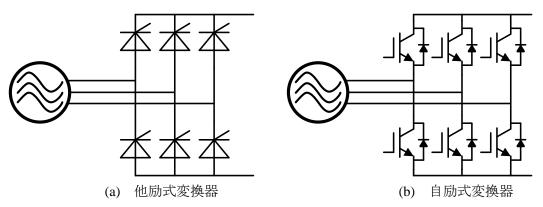

図 2.2 他励式変換器と自励式変換器の構成例

#### 2.1.3. HVDC 送電用電力変換器の方式

HVDC 送電に適用される電力変換器は、サイリスタを使用した他励式、IGBT などの自己 消弧機能を備えた半導体素子を使用した自励式に大別される。図 2.2 に他励式変換器と自励 式変換器の構成例を示す。HVDC 送電の初期段階では、他励式変換器が使用されていたが、IGBT の大容量化と低損失化が進められた近年では、自励式変換器が主流になりつつある(3)。表 2.2 に他励式変換器と自励式変換器の比較を示す。他励式変換器では、使用する半導体素子にターンオンの機能がなく、接続される系統電圧の位相に合わせて電流が転流する。したがって、系統電圧がない場合には送電動作(ブラックスタート)ができない。また、前述の通り、スイッチング周期は系統周波数と同じになるため多くの高調波を発生させることとなり、無効電力を制御することもできないため自励式変換器に比べて大規模なフィルタ設備

| 項目       | 他励式変換器       | 自励式変換器       |

|----------|--------------|--------------|

| 半導体素子    | サイリスタ        | IGBT         |

| ブラックスタート | 不可           | 可            |

| フィルタ設備   | 高調波を多く発生させるた | 他励式より高調波の発生が |

|          | め必要          | 小さいため,大規模なフィ |

|          |              | ルタは不要        |

| 調相設備     | 無効電力の供給が不可能で | 有効電力と無効電力を独立 |

|          | あるため、調相設備による | して制御できるため不要  |

|          | 補償が必要        |              |

| 損失       | 小            | 他励式に比べて大     |

| 大容量化     | 容易           | 他励式に比べて難しい   |

表 2.2 他励式変換器と自励式変換器の比較(5),(6),(8)~(10)

と調相設備が必要となる。その一方で、サイリスタは IGBT に比べて大電流が導通可能であり導通時の損失も小さく抑えることができる。したがって、他励式変換器の方がより大容量の電力を送電する用途で使用されている。しかし近年では、IGBT の大容量化も進んでおり、自励式変換器の送電電力も増加している(5),(6),(8)~(10)。

#### 2.2. 適用を想定する電力系統の構成

#### 2.2.1. HVDC 送電用自励式変換器

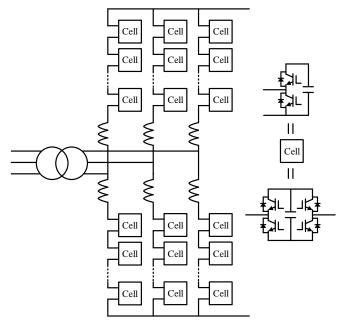

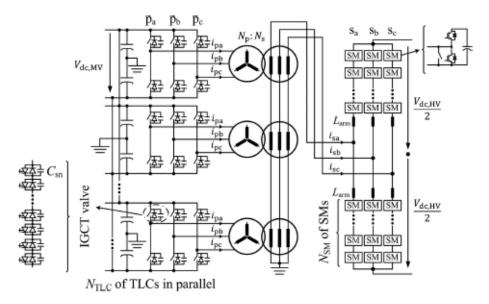

第1章でも説明したように洋上風力発電においては、陸上に先行して HVDC 送電の適用が進んでいる。これは、洋上に設置される洋上変換所から陸上までを海底ケーブルにより送電するため、より短い距離で HVDC 送電のコスト面でのメリットが発揮できるためである。また、洋上変換所の建設コストを抑制するために電力変換器としては、フィルタ設備や調相設備の不要な自励式変換器が適している。図 2.3 に洋上変換所に設置される自励式変換器の構成例を示す。この電力変換器は MMC(Modular Multilevel Converter)と呼ばれており、コンバータセル(セル)またはサブモジュールと呼ばれる変換器を多数直列に接続して1アームを構成しており、各セルを制御することで交流電圧を作り出す方式である(12),(13)。セル数を増加させることで簡単に出力する交流電圧のレベル数を上げられ、より正弦波に近い波形を出力できるためフィルタ設備が不要になるといった利点があり小型化の期待ができる。実際に MMC 型の変換器を採用することで、電力変換器の設置面積を他励式変換器や他方式の自励式変換器に比べて 58%低減できるといった報告もある(14)。以上から、今後の HVDC 送電に MMC 型変換器の導入が進められるものと考えられる。

図 2.3 洋上変換所に設置される自励式変換器の構成例(MMC)

#### 2.2.2. 洋上風力発電における直流化の動向

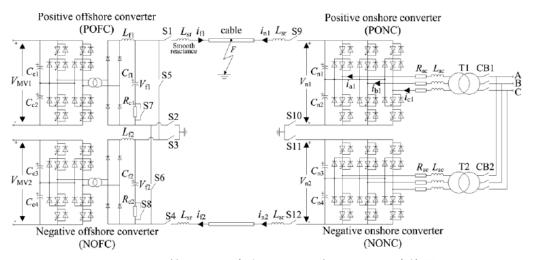

洋上風力発電において、発電コストを低減するために風車を大型化し、発電機単機の発電量を増加させる傾向がある。これに伴って、発電機から洋上変換所までの系統(集電系統)では、電流が増加することになり損失の増加が懸念される。このような背景から、集電系統における電圧を現在主流の交流 33kV から交流 66kV に高圧化検討されている<sup>(15)</sup>。また、さらなる高効率化を目的に集電系統おいても数十kV の直流(中圧直流または MVDC)を適用することが検討されている<sup>(16)-(22)</sup>。

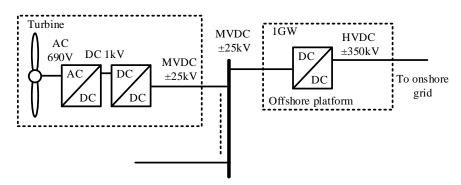

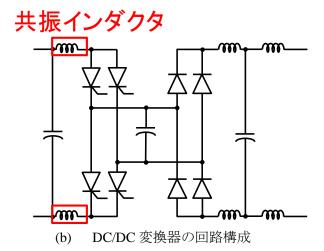

図 2.4 に現在主流の洋上風力発電システムの構成例を示す(22)-(24)。現在の洋上風力発電では、発電機の出力電圧は 690V 程度であり、風車内部で一度 AC/DC 変換器にて整流し再度 DC/AC 変換器で交流に変換した後に、変圧器により 33kV に昇圧し集電系統に連系している。図 2.4 中に示す洋上変換所における AC/DC 変換器が図 2.3 に示した MMC 型変換器である。一方で、集電系統に MVDC を適用した場合は図 2.5 に示すシステム構成を想定している(22)。このシステムでは、発電電力を風車内で 1kV 程度の直流から DC/DC 変換器で MVDC(±25kV)に昇圧し集電系統に連系する。その後、洋上変換所に設置する高圧 DC/DC 変換器にて HVDC(±350kV)に昇圧し陸上に送電される。文献(22)では、1kV を±25kV に昇圧する 10MW の DC/DC 変換器が提案されており、定格運転時の変換効率は 98.5%である。

図 2.6 に文献(16)にて提案されているシステム構成を示す。この構成では、各風車の DC/DC 変換器の出力を直列接続することで、変換器と変圧器での電力変換を 1 段削減している。また、 DC/DC 変換器へ SiC-JFET を適用することで最大変換効率は 98%を超える。 しかし、 集電は HVDC で行う必要があるため、HVDC ケーブルでの集電が必要であり、コスト面の課題がある。

次に、図 2.7 に文献(21)にて提案されているシステム構成を示す。この構成では、図 2.6 で

示したシステムと異なり、MVDCで集電し HVDCで送電するシステムである。このシステムでは、集電用ケーブルを AC ケーブルと同一損失にすることで重量を低減することを想定している。さらに、変換効率は 96.6%を達成している。しかしながら、非絶縁型の回路構成でありケーブルの地絡事故を考えると課題がある。さらに、文献(25)でも図 2.7 と同様に MVDCで集電し HVDCで送電するシステムが議論されているが、文献(22)と同じく非絶縁型の回路構成である。

図 2.4 現在主流の洋上風力発電システムの構成例(22)~(24)

図 2.5 集電系統に MVDC を適用した場合のシステム構成(22)

(a) システム構成

(b) DC/DC 変換器の回路構成

図 2.6 文献(16)にて提案されているシステム構成と DC/DC 変換器の回路構成

(a) システム構成

図 2.7 文献(21)にて提案されているシステム構成と DC/DC 変換器の回路構成

#### 2.2.3. 適用を想定する電力系統の構成

一方で、図 1.9 に示した次世代の電力系統のように、洋上風力発電だけでなく、陸上においても再生可能エネルギーの連系や家庭などの需要家も含めてすべての電力を直流で連系する構想が提案されている(26),(27)。この構成では、HVDC、MVDC、LVDC の 3 種類の直流系統が構成されている。このように今後の電力系統の移り変わりの中で、直流を使った送配電が頭角を現した際には、異なる電圧クラス間の電力変換が求められると想定される。

以上から、本研究において検討する高圧 DC/DC 変換器は、図 1.9 に示す電力系統に適用することを想定し、具体的には MVDC と HVDC の間で高効率な電力変換を実現できる高圧 DC/DC 変換器の実現を目的とする。

図 2.8 送配電を直流で行うことを想定した電力系統(27)

(出典: R. W. De Doncker: "Power Electronics Technologies for Flexible DC Distribution Grids", in Proc. of The 2014 International Power Electronics Conference (IPEC-Hirosima2014 – ECCE ASIA), pp. 736-743 (2014))

#### 2.3. 高圧 DC/DC 変換器の電気的仕様

高圧 DC/DC 変換器は MVDC と HVDC の間で高効率な電力変換を行う電力変換器である。 先行研究では、DC/DC 変換器の回路方式として絶縁型と非絶縁型の双方が検討されている。 ここで、高圧 DC/DC 変換器は数百 kV の高電圧を扱う電力変換器であることを踏まえると、 安全面と構成する部品の対地絶縁の観点から絶縁型の電力変換器であることが望ましいと 考えられる<sup>(27)</sup>。また、文献(22)を参考に MVDC 電圧を±25kV に設定し、HVDC 電圧を± 350kV に設定する。さらに、前述の通り風力発電機の単機当たりの定格電力が増加している ことを踏まえて高圧 DC/DC 変換器の定格電力を 1000MW とし、変換効率の目標値は文献 (22)を参考に定格運転時 98.5%以上に設定する。さらに、図 1.9 に示したようなすべて直流 化された電力系統への適用を想定しており、MVDC を介した蓄電池システムの活用や MVDC 側に設置した蓄電池システムとメガソーラなどの活用も想定される<sup>(28)</sup>。この場合、 MVDC から HVDC への送電動作と HVDC から MVDC への送電動作の双方向動作が必要と なることになる。

表 2.3 に上記に示す高圧 DC/DC 変換器の電気的仕様を整理した。以下,本研究において表 2.3 に示す電気的仕様を満足する高圧 DC/DC 変換器の提案を行う。

| 項目          | 仕様      |

|-------------|---------|

| 方式          | 絶縁型     |

| 送電方向        | 双方向     |

| MVDC 電圧     | ±25kV   |

| HVDC 電圧     | ±350kV  |

| 変換器容量       | 1000MW  |

| 目標効率(定格運転時) | 98.5%以上 |

表 2.3 高圧 DC/DC 変換器の電気的仕様

#### 2.4. 高圧 DC/DC 変換器の回路方式

表 2.3 に示した電気的仕様を満足する高圧 DC/DC 変換器の回路構成として検討されている先行例は、MMC 型変換器をベースとした FTF(Face-to-Face)方式と DAB(Dual-Active Bridge)コンバータを多数直列または並列に接続した DAB 方式に大別できる(28)-(34),(36),(37)。以下では、先行例を示しつつ各方式における課題を整理し、高圧 DC/DC 変換器の回路方式の方向性を示す。

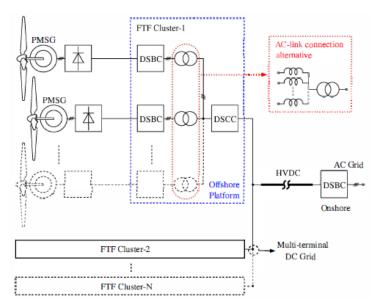

#### 2.4.1. FTF 方式の先行研究

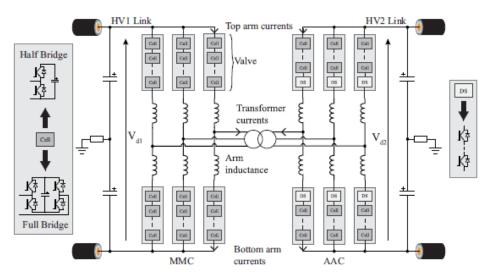

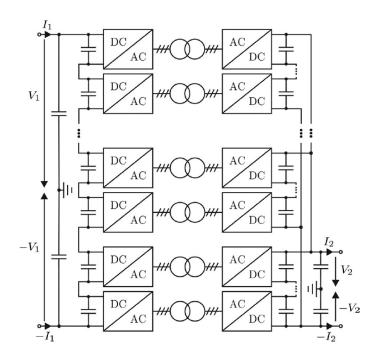

図 2.9 に文献(29)で提案されている FTF 方式の高圧 DC/DC 変換器の回路構成を示す。この構成では、現在 HVDC 送電用電力変換器として主流の MMC 型変換器を変圧器を介して交流でリンクさせる方式である。電流が大きくなる MVDC 側では MMC を並列に接続しており、HVDC 側の MMC は変圧器で昇圧した後の HVAC を HVDC に変換している。 MMC 型変換器は、前述の通り、先行して HVDC 送電に HVAC と HVDC との間で電力変換をおこなう AC/DC 変換器として採用されているため、電圧制御法などの基本的な制御方式は既に確立されている。したがって、2 台の MMC 型変換器を交流でリンクさせる回路構成である FTF 方式の高圧 DC/DC 変換器は実現のハードルが比較的低い。しかし、原理的に半導体素子がハードスイッチングになる点と、各セルの直流コンデンサには基本波成分が流入するため比較的大きなコンデンサ容量が必要となるという課題がある。

図 2.10 に文献(30)で提案されている FTF 方式の高圧 DC/DC 変換器の回路構成を示す。この方式では、片方の MMC の各アームに Director Switch (DS)を追加している点で図 2.9 の構成と異なっている。追加された DS の機能として電流の極性に合わせて導通するアームを選択しており、DS を追加することで各セルが出力する電流は MMC が出力する電流の半波分のみとなる。したがって、直流コンデンサの必要容量の低減と半導体素子の導通損失が低減できる。しかし、DS は半導体素子を複数直列に接続した構成であり、DS における導通損失とターンオフ時の各素子間の電圧バランスが課題となる。

図 2.11 に文献(31)で提案されている FTF 方式の高圧 DC/DC 変換器の回路構成を示す。この方式では、両側を単相の MMC としており、変圧器には 2 レベルの電圧を印可すること

で、DAB コンバータと同様な動作をさせる方式である。DAB コンバータでは、後述するように ZVS(Zero-Voltage Switching)動作が期待できるが、この方式では MMC 型変換器特有の循環電流の影響で ZVS 動作が発生できないと考えられ、DAB コンバータほど高く変換効率は期待できないと考えられる。

図 2.9 文献(29)で提案されている FTF 方式の高圧 DC/DC 変換器

図 2.10 文献(30)で提案されている FTF 方式の高圧 DC/DC 変換器

図 2.11 文献(31)で提案されている FTF 方式の高圧 DC/DC 変換器

#### 2.4.2. DAB 方式の先行研究

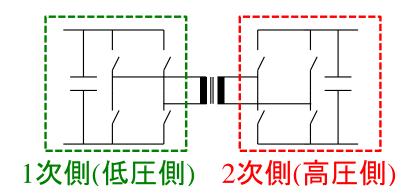

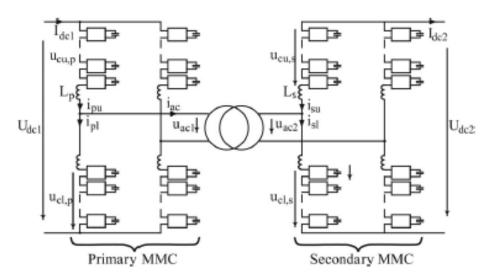

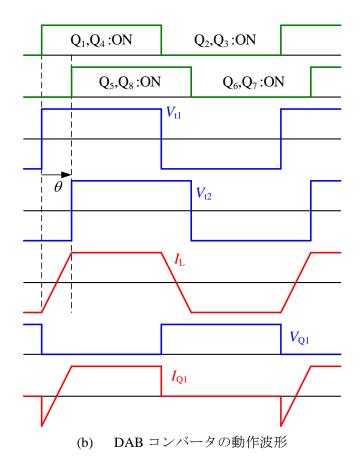

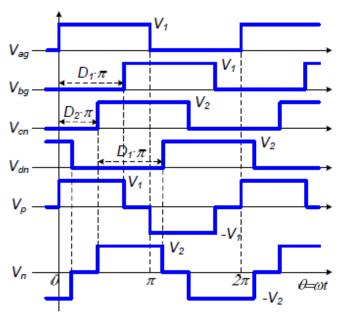

具体的な回路方式を説明するために DAB コンバータについて説明する。図 2.12 に DAB コンバータの回路構成と,動作波形を示す。DAB コンバータでは,電流経路のインダクタンスの作用により電圧の変化に対して電流の変化が遅れることを利用して,図 2.12 に示すように半導体素子を電圧がゼロの状態でターンオンさせる ZVS 動作が実現できるためターンオン損失が発生しない $^{(35)}$ 。したがって,高周波化による変圧器に小型化と高効率動作の両立が期待できる回路方式である。また,前述のインダクタンスについては,変圧器の漏れインダクタンスを利用することも可能であり,部品点数の削減も期待できる。送電電力は変圧器に印加される交流電圧  $V_{11}$  と  $V_{12}$  の位相差 $\theta$ によって制御される。

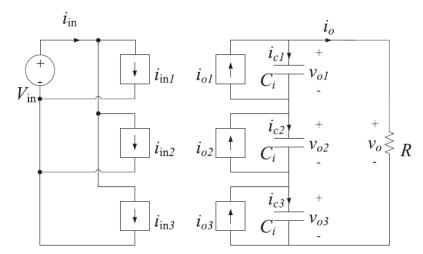

図 2.13 に文献(36)で提案されている DAB 方式の高圧 DC/DC 変換器を示す。この方式は、DAB コンバータを入力側並列接続、出力側直列接続されている方式である。この構成では DAB コンバータの直列数を調整することで容易に高電圧の出力を得ることができる。しかしその反面、入力側は半導体素子の耐圧上、高圧化することができない。現在の半導体素子の最高の耐電圧は 6.5kV であるが、実用上は、信頼性の観点からこの耐電圧の 50~60%程度で使用することが半導体素子メーカから推奨されていることを踏まえると、図 2.13 の方式では、入力電圧を 3~4kV 程度設いしなければならず、数十 kV の MVDC に対応できない。以上から、表 2.3 に示す入力電圧の仕様を満足させることができない。 DAB 方式の高圧 DC/DC 変換器としては、図 2.13 に示すような多数の DAB コンバータの入力並列出力直列 (IPOS)接続にした構成が提案されており、3 相構成の DAB コンバータを適用した構成も検討されている(37)が、図 2.13 に示す高圧 DC/DC 変換器と同じく入力側は半導体素子の耐圧上、高圧化することができないため表 2.3 に示す入力電圧の仕様を満足できない。一方で、文献(38)では、図 2.14 に示すような多数の DAB コンバータの 1 次側で直列接続、2 次側で直列したものをさらに並列接続した構成が提案されている。

(a) DAB コンバータの回路構成

図 2.12 DAB コンバータの回路構成と動作波形

図 2.13 文献(36)で提案されている DAB 方式の高圧 DC/DC 変換器

図 2.14 文献(38)で提案されている DAB 方式の高圧 DC/DC 変換器

図 2.14 の構成では、2 次側で直列と並列を組み合わせた構成であるため、図 2.13 に示す構成とは異なり、MVDC にも対応可能であり高圧 DC/DC 変換器の回路構成として有効なものと考えられる。しかし、詳しくは第3章で説明するが、直列接続と並列接続を MVDC 側で組み合わせ、出力側ですべて直列接続した構成とすると電圧制御の自由度が不足し、各DAB コンバータの電圧バランス制御が実現できないという課題がある。また、多数のDABコンバータを使用するという構成上DABコンバータと同数の変圧器が必要となりシステムの大型化が懸念される。

#### 2.4.3. その他の方式

FTF 方式および DAB 方式のほかにもいくつか提案されている。図 2.15 に文献(39)で提案されている高圧 DC/DC 変換器の構成を示す。この方式は、DAB 方式に近いが、2 次側をダイオード整流器で構成した SAB(Single-Active Bridge)コンバータを IPOS 接続した構成である。DAB コンバータと同様に SAB でも ZVS 動作による高効率化が期待できる。しかし、表 2.3 に示す電気的仕様の内で双方向への送電動作を実現することはできない。

次に、図 2.16 に文献(28)で提案されている高圧 DC/DC 変換器の回路構成を示す。この構成は、DAB 方式と FTF 方式のハイブリッドのような構成となっており、MVDC 側の変換器を 3 レベル変換器、HVDC 側の変換器を MMC とした構成である。この構成では、MVDC 側の変換器は DAB コンバータのように動作するため ZVS 動作が可能である。また、HVDC

図 2.15 文献(39)で提案されている高圧 DC/DC 変換器

図 2.16 文献(28)で提案されている高圧 DC/DC 変換器

側の MMC で電流制御を行うことで、直流電圧と変圧器の巻き数比の関係が崩れた場合の損失増を抑制することができる。DAB コンバータは、変圧器と 2 台のフルブリッジから構成されており、変圧器に巻線にはそれぞれのフルブリッジから電圧が印加される。そのため、直流電圧と変圧器の巻き数比の関係が等しい場合に最も ZVS 動作領域が広くなり高効率な動作が実現できる(35)。しかし、MVDC 側および HVDC 側の電圧に変動が発生した場合、直流電圧と変圧器の巻き数比の関係が崩れ、変圧器電流の電流ピーク値や実効値が増加し変換効率が低下するという課題がある。そこで、図 2.16 に示すように片側を MMC にすることで変圧器電流の電流制御ができるため、前述の課題を解決することが期待できる。しかし、MMC は前述の通り半導体素子がハードスイッチングとなるため変換効率の観点で課題が残る。

表 2.4 に本章で紹介した高圧 DC/DC 変換器の回路構成について長所と課題を示す。本研究では、高効率な高圧 DC/DC 変換器の実現を目的としている。FTF 方式やハイブリッド構成では、電圧制御法が確立しており実現性は高いが、半導体素子がハードスイッチングとなるため高効率化が難しいという課題がある。一方で、高効率化が期待できる DAB 方式では、半導体素子耐圧の制約があり、電圧制御の自由度が不足する点や多数の変圧器を使用する点が課題となる。本研究では、表 2.4 に示した長所と課題を踏まえたうえで最も実現性の高い FTF 方式と高効率化が期待できる DAB 方式に絞って比較検討を行うこととする。

表 2.4 本章で紹介した高圧 DC/DC 変換器の回路構成について特徴と課題

| 方式 | FTF方式          | DAB 方式         | その他の方式           |

|----|----------------|----------------|------------------|

| 特徴 | 複数台の MMC 型変換器  | 複数台の DAB コンバー  | ・SAB コンバータを IPOS |

|    | を交流でリンクさせる     | タを IPOS 接続または直 | 接続する             |

|    |                | 並列を組み合わせて接続    | ・FTF 方式と DAB 方式の |

|    |                |                | ハイブリッド構成         |

| 長所 | 現在の HVDC 用変換器と | ・ZVS 動作による高効率  | ZVS 動作による高効率化    |

|    | して主流であり、制御法    | 化が期待できる        | が期待できる           |

|    | 等確立しているため最も    | ・高周波化による変圧器    |                  |

|    | 実現性が高い         | の小型化が期待できる     |                  |

| 課題 | ・半導体素子がハードス    | ・IPOS 接続の場合,半導 | ・SAB コンバータを用い    |

|    | イッチングとなるため損    | 体素子耐圧の制約上      | た構成では双方向の送電      |

|    | 失大             | MVDC への対応が不可能  | 動作が不可能           |

|    | ・大容量の直流キャパシ    | ・直並列接続を組み合わ    | ・FTF 方式と DAB 方式の |

|    | タが必要           | せた構成では電圧制御の    | ハイブリッド拘泥では,      |

|    |                | 自由度が不足する       | MMC 側の素子がハード     |

|    |                | ・DAB コンバータと同数  | スイッチングとなり損失      |

|    |                | の変圧器が必要となりシ    | 大                |

|    |                | ステムが大型化する      |                  |

#### 2.5. まとめ

本章では、HVDC 送電に関す技術的背景を説明しつつ、HVDC 送電の優位性を明らかにした。 さらに、HVDC 用変換器の方式である他励式と自励式の比較を行った。また、洋上風力発電を例に集電系統に MVDC の適用が検討されていることを紹介し、さらに、洋上風力発電のみならず、すべて直流化された電力系統の構想があることを説明した。本研究で検討する高圧 DC/DC 変換器の適用先もすべて直流化された電力系統であり、このことから必要となる電気的仕様について整理を行った。また、電気的仕様を満足することが期待できる変換器方式について先行研究を具体例として特徴、長所、課題を整理した。結果、候補となり得る回路方式として FTF 方式と DAB 方式であることが明らかとなった。本章以降では、前記 2 方式を中心に検討を行い、高圧 DC/DC 変換器の回路方式を決定する。

# 参考文献

- (1) 国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO): 「直流送電技術における NEDO の取組」 (2019)

- (2) ABB 社 HP: https://new.abb.com/systems/hvdc/references/the-gotland-hvdc-link (2019)

- (3) M. Davies, M. Dommaschk, J. Dorn, D. Retzmann, and D. Soerangr: "HVDC PLUS Basics and Principle of Operation", SIEMENS Technical article (2009)

- (4) ABB 社 HP: https://new.abb.com/systems/hvdc/why-hvdc (2019)

- (5) 横山明彦:「直流送電技術の現状と課題および将来への展望」,電気学会誌, Vol. 137,No. 11, pp.745-746 (2017)

- (6) 宜保直樹・高崎昌洋:「直流送電技術」, 電気設備学会誌, Vol. 32, No. 12, pp.869-872 (2012)

- (7) SIEMEN 社 HP:

- (8) https://pdfs.semanticscholar.org/c6fe/55531b61d7e3c8d71024bbef23516042bd4a.pdf (2019)

- (9) 国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO):「次世代洋上直流送電システム開発事業」, スマートコミュニティ部成果報告会資料 (2016)

- (10) 堀井博夫・飯村美起・桐原健太・早坂靖士・山邉和也:「送配電分野における監視制御 の取り組み」,日立評論, Vol. 99, No. 2, pp. 50-57 (2017)

- (11) 武田秀雄・吉野輝雄・桑原隆: 「自励式変換器による電力系統用パワーエレクトロニクスの適用拡大」, 東芝レビュー, Vol. 55, No. 8, pp. 16-19 (2000)

- (12) 電力広域的運営推進機関:「系統運用に関する基本用語の解説」,第3回平成30年北海 道北海道胆振東部地震に伴う大規模停電に関する検証委員会参考資料2 (2018)

- (13) 萩原誠・赤木泰文: 「モジュラー・マルチレベル変換器(MMC)の PWM 制御法と動作検証」, 電学論 D, Vol. 128, No. 7, pp. 957-965 (2008)

- (14) 菊間俊明・高崎昌洋: 「2 重 Y 結線モジュラーマルチレベル変換器の制御法」, 電学論 D, Vol. 133, No. 9, pp. 917-927 (2013)

- (15) RL. Sellick, and M. Akerberg: "Comparison of HVDC Light (VSC) and HVDC Classic (LCC) Site Aspects, for a 500MW 400kV HVDC Transmission Scheme", in Proc. of 10th IET International Conference on AC and DC Power Transmission (ACDC 2012), pp. 1-6 (2012)

- (16) 石原孟:「わが国における洋上風力発電実証研究の現状と将来展望」,環境管理, Vol.48, No.9, pp.11-17 (2012)

- (17) G. Ortiz, J. Biela, D. Bortis and J. Kolar, "1 Megawatt, 20 kHz, Isolated, Bidirectional 12kV to 1.2kV DC-DC Converter for Renewable Energy Applications," in Proc. of The 2010 International Power Electronics Conference –ECCE ASIA, pp. 3212-3219 (2010)

- (18) C. Meyer, M. Höing, A. Peterson and R. W. De Doncker, "Control and Design of DC-Grids for Offshore Wind Farms," *IEEE Trans. on Industry Applications*, Vol.43, No.6, pp.1475-1482 (2007)

- (19) D-M. Valcan, P. C. Kjær, L. Helle, S. Sahukari, M.H-Maharsi and S. Singh, "Cost of Energy Assessment Methodology for offshore AC and DC wind power plants," in Proc. of Optimization of Electrical and Electronic Equipment (OPTIM), pp. 919-928 (2012)

- (20) S. C. Raval, R. Botta and H. N. Raval, "Comparison of energy production cost for MVAC and MVDC offshore wind farm distribution system," in Proc. of Energy, Power and Transportation Electrification (ACEPT), 2017 Asian Conference, pp. 1-6 (2017)

- (21) F. Blaabjerg and K. Ma, "Future on power electronics for wind turbine systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 1, Issue 3 (2013)

- (22) J. Robinson, D. Jovcic, and G. Joós: "Analysis and Design of an Offshore Wind Farm Using a MV DC Grid", *IEEE Trans. on Power Delivery*, Vol.25, No. 4, pp.2164-2173 (2010)

- (23) T. Jimichi, M. Kaymak and R. W. De Doncker, "Desgin and loss analysis of a medium-voltage DC-DC converter intended for offshore wind farms," in Proc. of 2016 IEEE International Conference on Renewable Energy Research and Applications (ICRERA), pp.137-142 (2016)

- (24) Y. Sang, A. J. Tim, and C. Green: "Transformer Design in a Medium Voltage DC/DC Converter for a DC Collection Network," in Proc. of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), pp. 1-10 (2017)

- (25) F. Blaabjerg, M. Liserre, and K. Ma: "power electronics converters for wind Turbine Systems," *IEEE Trans on Industry Applications*, Vol. 48, No. 2, pp. 708-719 (2012)

- (26) W. Chen, A. Huang, S. Lukic, J. Svensson, J. Li, and Z. Wang: "A Comparison of Medium Voltage High Power DC/DC Converters with High Step-up Conversion Ratio for Offshore Wind Energy System", in Proc. of 2011IEEE Energy Conversion Congress and Exposition (ECCE), pp.584-589 (2011)

- (27) R. W. De Doncker: "Power Electronics Technologies for Flexible DC Distribution Grids", in Proc. of The 2014 International Power Electronics Conference (IPEC-Hirosima2014 –ECCE ASIA), pp. 736-743 (2014)

- (28) M. J. Carrizosa, A. Benchaib, P. Alou, and G. Damm: "DC transformer for DC/DC connection in HVDC network", in Proc. of 2013 15th European Conference on Power Electronics and Applications (EPE), pp. 1-10 (2013)

- (29) S. Cui, N. Soltau and R. W. De Doncker, "A High Step-up Ratio Soft-switching DC-DC Converter for Interconnection of MVDC and HVDC Grids," IEEE Trans on Power Electronics, Vol. 33, No. 4, pp.2986-3001 (2018)

- (30) F. Sasongko, M. Hagiwara and H. Akagi, "A Front-to-Front (FTF) System Consisting of Multiple Modular Multilevel Cascade Converters for Offshore Wind Farms," in Proc. of The 2014 International Power Electronics Conference (IPEC-Hirosima2014 –ECCE ASIA), pp. 1761-1768 (2014)

- (31) A. Schön and M-M. Bakran, "High Power HVDC-DC converters for the interconnection of HVDC

- lines with different line topologies," in Proc. of The 2014 International Power Electronics Conference (IPEC-Hirosima2014 –ECCE ASIA), pp. 3255-3262 (2014)

- (32) S. Kenzelmann, A. Rufer, D. Dujic, F. Canales and Y. R. de Novaes, "Isolated DC/DC Structure Based on Modular Multilevel Converter," *IEEE Trans. on Power Electronics*, Vol.30, No.1, pp.89-98 (2015)

- (33) J. A. Ferreira, "The Multilevel Modular DC Converter," *IEEE Trans. on Power Electronics*, Vol.28, No.10, pp.4460–4465 (2013)

- (34) K. Koska, P. Blaszczyk, P. Klimczak, P. Halat and R. Jez, "Branch Energy Balancing of Double Wye DC-DC Modular Multilevel Converter," in Proc. of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), pp.1-10 (2017)

- (35) A. Gowaid, G. P. Adam, S. Ahmed, D. Holliday and B. W. Williams, "Analysis and Design of a Modular Multilevel Converter With Trapezoidal Modulation for Medium and High Voltage DC-DC Transformers," *IEEE Trans. on Power Electronics*, Vol.30, No.10, pp.5439-5457 (2015)

- (36) R. W. De Doncker, D. M. Divan and M. H. Kheraluwala, "A Three-Phase Soft-Switched High-Power-Density dc/dc Converter for High-Power Application," *IEEE Trans. on Industry Applications*, Vol.27, No.1, pp.63-73 (1991)

- (37) P. Zumel, L. Ortega, A. Lázaro, C. Fernández, A. Barrado, A. Rodríguez and M. María, "Modular Dual-Active Bridge Converter Architecture," *IEEE Trans. on Industry Application*, Vol.52, No.3, pp. 2444-2455 (2016)

- (38) M. Guan: "A Series-Connected Offshore Wind Farm Based on Modular Dual-Active-Bridge (DAB) Isolated DC-DC Converter", *IEEE Trans. on Energy Conversion*, Vol. 34, No. 3, pp. 1422-1431 (2019)

- (39) S. P. Engel, M. Stieneker, N. Soltau, S. Rabiee, H. Stagge and R. W. De Doncker, "Comparison of the Modular Multilevel DC Converter and the Dual-Active Bridge Converter for Power Conversion in HVDC and MVDC Grids," *IEEE Trans. on Power Electronics*, Vol.30, No.1, pp.124-137 (2015)

- (40) F. Deng and Z. Chen, "Operation and Control of a DC-Grid Offshore Wind Farm Under DC Transmission System Faults," *IEEE Trans. on Power Delivery*, Vol.28, No.3, pp.1356-1363 (2013)

- (41) F. Krismer, and J. W. Kolar: "Closed Form Solution for Minimum Conduction Loss Modulation of DAB Converters", *IEEE Trans. on Power Electronics*, Vol.27, No.1, pp.174-188 (2012)

# 第3章

# 高圧 DC/DC 変換器の回路構成と電圧制御法

再生可能エネルギーの更なる有効活用のためには、送電系統に高電圧直流(HVDC)を適用するだけでなく、配電系統においても中電圧直流(MVDC)を適用する必要があり、そのためには、HVDCと MVDC の間で電力変換を行う高効率な電力変換装置が必要となる。本章では、HVDCと MVDC の間で電力変換を行う高圧 DC/DC 変換器の基本回路構成を明らかにし、必要となる電圧バランス制御について検討する。

#### 3.1. 基本回路構成

### 3.1.1. DC システムの構成

図 3.1 に洋上風力発電を例とした MVDC で各風力発電機から洋上変換所までの集電(配電)を行い HVDC で陸上までの送電を行う洋上風力発電システムの構成例を示す。このシステムでは、発電した交流電力を風車内で LVAC(IkV 程度)から MVAC(数十kV)に変圧器で昇圧する。その後、洋上で複数の風車の出力を集電し、場合によっては、再度変圧器で昇圧して集電する方式が採用される。集電後の電力は、変圧器と AC/DC 変換器を用いて HVDC に変換され陸上に送電される。しかし、前述のように洋上風力発電の大規模化に伴う損失増加に対処すべく、図 3.1 に示すような DC 集電および HVDC 送電を行う DC システムの適用が検討されている。DC システムでは、発電電力を風車内で LVDC(IkV 程度)から中圧 DC/DC変換器で MVDC へ昇圧する。その後、洋上で複数の風車出力を集電し、洋上変換所に設置する高圧 DC/DC 変換器にて HVDC に昇圧し陸上に送電される。したがって、洋上変換所の高圧 DC/DC 変換器には、MV/HV 間の電気的絶縁と高効率の電力変換が求められる。

図 3.1 直流による洋上風力発電システム

#### 3.1.2. 高圧 DC/DC 変換器の回路構成比較

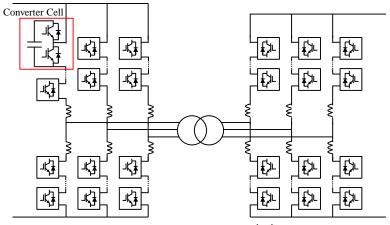

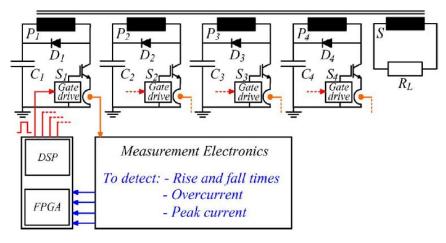

前述のように,高圧 DC/DC 変換器には MV/HV 間の電気的絶縁と高効率の電力変換が要求さ れる。図 3.2 にこれらの観点から考えられる、高圧 DC/DC 変換器の主回路構成例を示す。図 3.2(a) に示す FTF(Front-to-Front)方式は、現在の HVDC 送電システム に 良 く 使 用 さ れ て い る MMC(Modular Multilevel Converter)2 台から構成されており、交流リンク電圧を高周波化するこ とでシステムの小型化が可能である(1)。さらに、各変換器セルに内在するキャパシタの電圧 制御方式なども既に確立しており、実現の技術的ハードルは比較的低い。しかし、変換器を 構成する半導体の電流は原理的に直流成分と交流成分の合計値であり,各変換器セルの出 力電圧も直流成分と交流成分の合計値となるため、半導体素子数が多くなるという課題が ある。一方で、図 3.2 (b)に示す DAB(Dual-Active Bridge)方式(2)は、FTF 方式と同様に高周波 化による変圧器の小型化が可能である。DAB 方式における半導体の電流や各セルの出力電 圧を考えると、交流成分のみとなるため、半導体素子数を抑えることができる。また、変換 器セルを多数直並列に接続することで容易に高圧 DC/DC 変換器の大容量化および高圧化が 可能である。さらに,後述する ZVS(Zero-Voltage Switching)動作を行うことでスイッチング 損失を低減できるため,効率面でも有利である。その一方で,DAB 方式では FTF 方式と比 較すると各セルに変圧器巻線が必要なことから、 変圧器数が多くなり、 システムの大型化が 懸念される。そこで,SVG (Static Var Generator)への適用実績がある多重変圧器⑶により,複 数台の変圧器を 1 つの主鉄心と複数の巻線で構成することでシステムの大型化を抑えるこ とができ、課題を解決可能である。以上から、本学位論文では高圧 DC/DC 変換器の主回路 構成として図3.2(b)に示す DAB 方式としている。

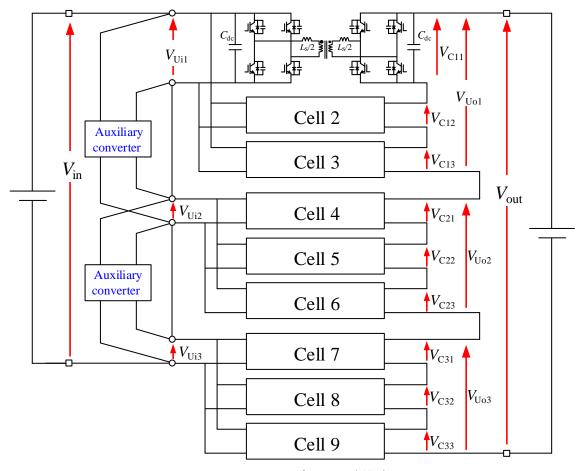

## 3.1.3. 提案する高圧 DC/DC 変換器の回路構成

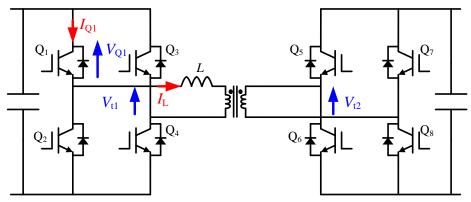

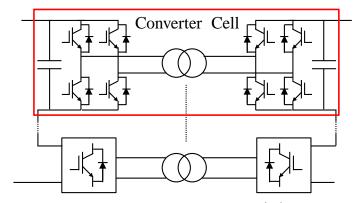

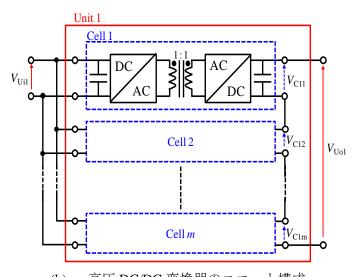

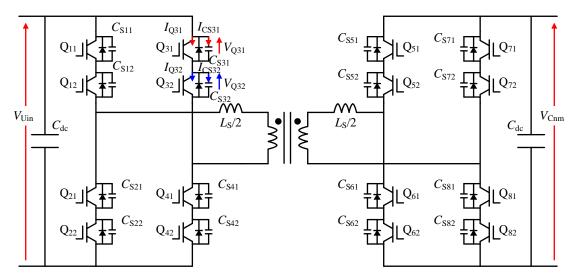

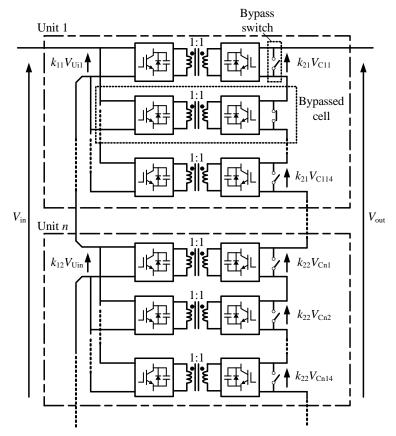

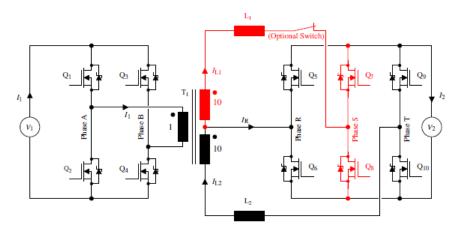

図 3.3 に提案する高圧 DC/DC 変換器の主回路構成を示す。図 3.3 に示すように、高圧 DC/DC 変換器は、前述の DAB 方式であり、DC/AC 変換器 2 台と変圧器から構成される双方向絶縁型 DC/DC 変換器を m×n 台使用している。また、m台のセルを電流が大きい MVDC 側で並列に接続、高圧化されている HVDC 側で直列に接続して 1 つの変換器ユニットを構成し、これを n 台直列に接続している。さらに、ユニット同士を直列に接続することで、HVDC 側では全てのセルが直列接続となり、MVDC 側では直列・並列に接続される。このような構成にすることで、MVDC および HVDC の電圧に対応することができる。一方で、ユニット単位で考えると、MVDC 側で並列・HVDC 側で直列の構成である。したがって、ユニット内のセル数 m を調整することで、容易に高い昇圧比を得ることができる。さらに、詳細は後述するが、各ユニットの入力側に電圧制御用の補助変換器を接続している。一般的に、送電損失を低減するために、送電電圧が高圧化されることを踏まえると、MVDC および HVDC は非常に高圧になることが想定されるが、半導体素子の耐圧は限られており、高圧化には限界がある。一方で、図 3.3 に示す主回路構成にすることで、MVDC 側・HVDC 側でともにユニットが直列に接続されているため MVDC および HVDC を半導体素子の耐圧以上に設定することが

(a) FTF(Front-to-Front)方式

(b) DAB(Dual-Active Bridge)方式

図 3.2 高圧 DC/DC 変換器の主回路構成例

可能になり、集電・送電における損失を低減することができる。さらに、電力系統に連系するような商用周波数の大容量変圧器は、非常に大きな体積・重量を持つが、図 3.3 の主回路構成では、ZVS によるスイッチング損失抑制が見込めるため、高周波化による変圧器の小型化が期待できる。一方で、電圧制御方式については、高電圧大容量の電力変換器としてよく知られている MMC では、電流・電圧を検出し座標変換を繰り返した後に各セルの指令値を得る方式であることに対して、詳細は後述するが、本学位論文では、電圧のみを検出し制御器を介して指令値を得る簡単な方式である。

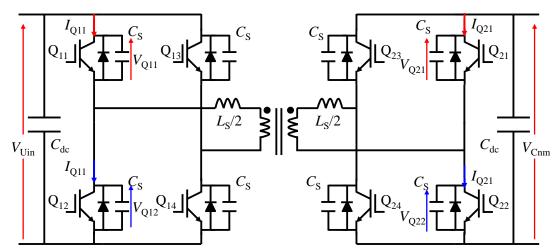

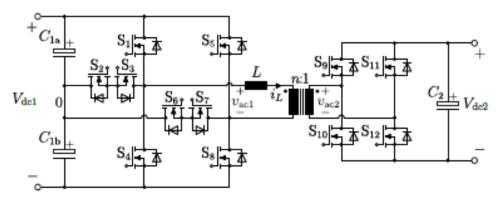

図 3.4 に高圧 DC/DC 変換器を構成する最小の変換器単位であるセルの回路構成を示す。 図 3.4 に示すセルは 2 台のフルブリッジ回路と 1 台の変圧器から構成された DAB 方式の DC/DC 変換器(以下, DAB コンバータ)であり、全てのスイッチング素子にはスナバキャパシタ  $C_S$  を並列に接続している。さらに、図 3.4 中の  $L_S$  は変圧器の漏れインダクタンスを表しており、1 次側および 2 次側にそれぞれ均等に配置している。DAB コンバータの特長として、特別な制御なしに ZVS 動作を実現し、左右対称の構造のため送電方向にかかわらず同様の制御を行うことが可能である。つまり、DAB コンバータは、180 度通電の矩形波電圧 を変圧器の 1 次側および 2 次側にそれぞれのフルブリッジから出力し、変圧器の 1 次側および 2 次側に印加される矩形波電圧の位相差 $\theta$ により以下に示す式で送電電力  $P_{DAB}$  が制御できる $^{(4),(5)}$ 。

$$P_{\text{DAB}} = \frac{V_{\text{Uin}}V_{\text{Cnm}}}{\omega L_{\text{S}}} \theta \left(1 - \frac{\theta}{\pi}\right)$$

(3.1)

ただし、(3.1)式において  $V_{\text{Uin}}$  はセル 1 次側電圧、 $V_{\text{Cnm}}$  はセル 2 次側電圧、 $\omega = 2\pi f_{\text{sw}}$  であり、 $f_{\text{sw}}$  は  $Q_{11} \sim Q_{24}$  のスイッチング周波数である。また、位相差 $\theta$ は $-\pi/2$  から $\pi/2$  までの範囲で動作可能であり、1 次側に対する 2 次側の位相差が $\theta$ -0 の時は 1 次側から 2 次側への送電、 $\theta$ <0 の時は 2 次側から 1 次側への送電動作を行う。このように、双方向の電力変換を行う構成

(a) 高圧 DC/DC 変換器の全体回路構成

(b) 高圧 DC/DC 変換器のユニット構成

図 3.3 提案する高圧 DC/DC 変換器の回路構成

図 3.4 高圧 DC/DC 変換器におけるセルの回路構成

とすることで、システム起動時やメンテナンス時に必要となる電力を変換器によって陸上から供給できるようになるため、送電系統を別途敷設する必要がなくなる $^{(0)}$ 。さらに、変圧器の漏れインダクタンスを適切に設計することで、変圧器に直列にインダクタンスを追加する必要が無くなり、部品点数の削減が可能となる。したがって、本章における DAB コンバータの  $L_{\rm S}$  は、変圧器の漏れインダクタンスを使用する。

また、DAB コンバータは、1 次側と 2 次側の直流電圧が等しい時に最も ZVS 可能領域が広くなることが知られており、高周波化によるスイッチング損失の増加が抑制できる $^{(7)}$ 。したがって、高効率を維持しながら、高周波化による変圧器の小型化を達成することができる。以上のことから、 図 3.4 に示すセルの 1 次側直流電圧  $V_{Uin}$  と 2 次側  $V_{Cnm}$  を等しい値とし、変圧器の巻数比も 1:1 としている。

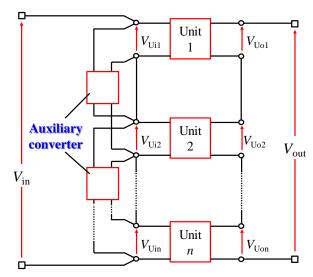

## 3.2. 高圧 DC/DC 変換器の電圧制御法

#### 3.2.1. 電圧バランス制御

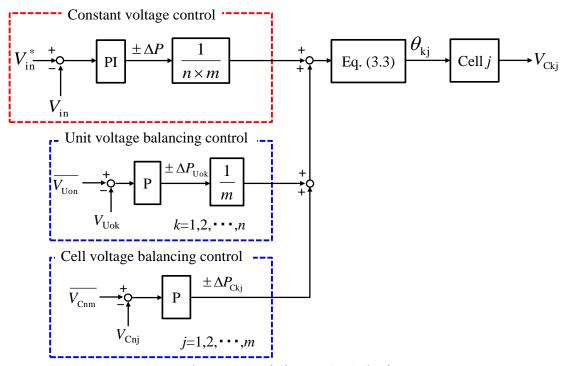

図 3.5 に高圧 DC/DC 変換器における電圧制御ブロックを示す。電圧制御は、高圧 DC/DC 変換器の入力電圧である MVDC 側の直流電圧  $V_{\rm in}$  を一定にする電圧一定制御と各セルおよびユニットの出力電圧を均一に制御するバランス制御から構成されている。

一般的に、出力電圧を制御する DC/DC 変換器を複数台、入力側並列、出力側直列に接続する場合、出力側の電圧を均一に維持したまま運転することが可能であるが、本章で提案する高圧 DC/DC 変換器は、図 3.1 に示すように出力が変動する電源に接続することを想定している。そのため、変換器の入力側である集電系統の MVDC を一定に制御する必要がある。さらに、前述したように、図 3.4 に示す主回路構成では、MVDC を高圧化し集電系統での損失を低減するために、入力側でも各ユニットを直列に接続した構成となっている。DC/DC 変換器を入出力側ともに直列に接続した場合、出力インピーダンスの高い変換器に電圧集中が発生することが知られている(8)。また、本章で示すような、セルの入力並列、出力直列に

接続した構成となっているユニットでは,入力電圧の制御を行うとセル間で出力電圧のアンバランスが発生し安定に動作できないことも知られている。この課題に対して,本章では, $V_{in}$ の一定制御とユニットおよびセルの出力電圧バランスを 図 3.5 に示す電圧制御と後述する補助変換器により実現している。具体的には高圧 DC/DC 変換器全体の送電電力を制御することで  $V_{in}$ の一定制御を行い,ユニットおよびセル毎の出力電圧を全体の電圧平均値に一致するように個別に送電電力を調整することで出力電圧のバランス制御を実現している。一方で,ユニットの入力側も直列になっており,電圧バランス制御が必要となるが,既にユニットの送電電力は,ユニットの出力電圧バランス制御に使用しているため,ユニットの入力側の電圧バランスを実現するための自由度が不足している。そこで,前述の補助変換器をユニット入力側に接続し,電圧バランス制御を実現している。

ここで、ユニットおよびセルの出力電圧のバランス制御が集電系統の電圧一定制御に対して及ぼす影響について検討する。図 3.5 に示すように、電圧一定制御は電圧指令値  $V_{\rm in}$ \*と集電系統の電圧値  $V_{\rm in}$  を比較し、その差分に応じた電力指令値 $\pm\Delta P$  を PI 制御器を介して得ている。一方で、ユニットおよびセルの出力電圧のバランス制御は、出力電圧平均値との差分から P 制御器を介して電力指令を得ている。このような構成にすることで、ユニットおよびセルの出力電圧バランス制御を行う電力指令 $\pm\Delta P_{\rm Uok}$  および $\pm\Delta P_{\rm Ckj}$  の合計値はゼロになる。したがって、ユニットおよびセルの出力電圧バランス制御は高圧 DC/DC 変換器の送電電力量に無関係となる。

図 3.5 高圧 DC/DC 変換器の電圧制御ブロック

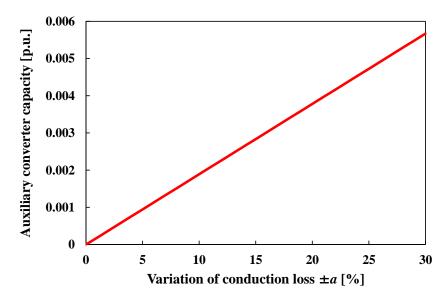

#### 3.2.2. 補助変換器の必要容量

ユニット間の送電電力のバラつき $\Delta P_{\text{Unit}}$ を生じさせる主な要因として考えられるのは、半導体損失  $P_{\text{SW}}$  のバラつきと  $L_{\text{S}}$  のバラつきに起因する送電電力のバラつき  $P_{\text{Ls}}$  ある。DAB コンバータは、ZVS 動作とスナバキャパシタの効果によりスイッチング損失は小さくなることを考えると、 $P_{\text{SW}}$  の主成分は導通損失となる。ここで、高圧 DC/DC 変換器の変換効率を $\eta\%$ とし、半導体損失のバラつきを $\pm a\%$ 、全損失に対する半導体損失の割合を  $r_{\text{sw}}\%$ とすると $P_{\text{SW}}$  は下記式で求めることができる。

$$P_{\rm SW} = 2 \left[ m \times P_{\rm DAB} \times \left( 100^{\%} - \eta^{\%} \right) \times r_{\rm SW}^{\%} \times a^{\%} \right]$$

(3.2)

ここで、前述のように  $P_{SW}$  の主成分は導通損失となることから、 $r_{SW}$  は全損失に対する導通損失の割合と考えられる。次に、 $L_S$  のバラつきの影響を検討する。 $L_S$  が他のセルに比べて大の場合、送電電力が低下するため各セルの HVDC 側の直流電圧が低下する。一方で、MVDC 側では、送電電力が低下したことで、MVDC 側の直流電圧  $V_{Uin}$  が増加する。このとき、電圧バランス制御により HVDC 側の直流電圧を上昇させるために、該当するセルの位相差を増やし送電電力が増加する。さらに、送電電力が増加することで  $V_{Uin}$  が低下する。以上から、 $L_S$  のバラつきによるユニット間の送電電力のバラつきは、電圧バランス制御により解消されるため、補助変換器は半導体損失に起因する電力のバラつきのみを負担すればよく $\Delta P_{Unit} = P_{SW}$  となる。

補助変換器の必要な容量を考えると、 $\Delta P_{\text{Unit}}$ がゼロになるように制御することから、(3.2) 式で求められるユニット間の電力差 $\Delta P_{\text{Unit}}$ の半分を融通すれば良い。ここで、容量は異なるが、DAB コンバータの損失分析が詳細に実施されている文献(7)を参考に半導体損失の割合を求める。文献(7)は 10kW 定格の DAB コンバータについて記載されており、定格送電時の全損失は 335W、変換効率は $\eta$ =96.65%である。全損失の内、導通損失が 189W であるから  $r_{\text{sw}}$ =56.42% となる。

図 3.6 に半導体損失のばらつき a を変数として、前述の変換効率 $\eta$ =96.65%で全損失に対する導通損失の割合  $r_{sw}$ =56.42%の場合に、必要となる補助変換器の変換器容量を算出した結果を示す。ただし、図 3.6 において算出した補助変換器の容量はユニットの変換器容量で規格化している。図 3.6 に示すように、補助変換器の容量は半導体損失のバラつき a に比例して増加し、 $a=\pm30$ %の時におよそ 0.0057 $p_{sw}$ . になる。ここで、本章では補助変換器の変換器容量について、文献(7)に示されている損失分析の結果に基づき算出した。しかし、実用上は、使用する半導体素子により導通損失の割合も変化するため、文献(7)に示されたように詳細な損失分析を実施したのちに算出されるものである。また、図 3.3 の変換器は、文献(7)に示された変換器に比べて、大容量であり、高耐圧の半導体素子の適用が想定されるため、高効率であり、導通損失の割合も小さくなることが想定される。したがって、本章で算出した補助変換器の変換器容量は実際に必要となるものに比べて大きく見積もられていることになる。しかし、この場合でも、変換器容量はユニット定格の 0.0057 $p_{sw}$ . であり非常

図 3.6 補助変換器の必要容量計算結果

図 3.7 補助変換器の制御ブロック

に小さいものとなることから、する高圧 DC/DC 変換器において、補助変換器の変換器容量は非常に小さくなることが示されている。

次に、補助変換器の配置について考える。補助変換器は直列接続になるユニット同士の電力バラつきをゼロに制御するため、MVDC 側および HVDC 側のどちらに接続してもよい。しかしながら、補助変換器の対地絶縁を考慮した場合、ユニットの出力側は HVDC 端子であるため、補助変換器にも HVDC に対応した対地絶縁が必要になる。以上から、本章で提案する高圧 DC/DC 変換器では、補助変換器を MVDC 側に配置する。

## 3.2.3. 補助変換器の制御法

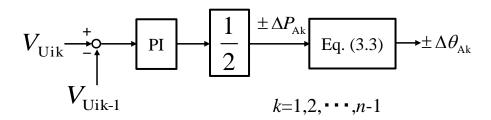

図 3.7 に補助変換器の電圧制御ブロックを示す。図 3.7 に示すように補助変換器によるユニットの入力側電圧のバランス制御は、補助変換器の入出力電圧である、ユニットの入力電圧それぞれを検出し、検出したユニットの入力電圧の差分を PI 制御器に入力することでバランスさせるための電力指令値を生成している。以上から、補助変換器では、ユニットの間の電力差を融通するだけであるため全体の電力制御には影響を与えない。なお、補助変換器の回路方式は、図 3.4 に示す DAB コンバータとしている。

#### 3.2.4. 位相差の算出方法

${\sf DAB}$  コンバータでは、電力を調整するために位相差 $\theta$ を制御しなければならない。ここで、実際の運転範囲を考慮して漏れインダクタンス  ${\it L}_{\rm S}$  を設計した場合、位相差 $\theta$ の変化範囲は小さくなることを考慮すると、(3.1)式を変形することで簡単に位相差 $\Delta \theta$ を算出することができる。

$$\Delta\theta \cong \frac{\omega L_{\rm S}}{V_{\rm DC}^2} \Delta P_{\rm DAB} \tag{3.3}$$

ただし、(3)式においてセルの入出力電圧が等しくかつ変圧器の巻数比が 1:1 であることから、 $V_{\text{Uin}} = V_{\text{Cin}} = V_{\text{DC}}$  としている。以上から、本章に示す電圧制御法では、電圧を制御するための電力 $\Delta P_{\text{DAB}}$  を送電するための位相差 $\Delta \theta$ を(3.3)式で求めることで実現している。

## 3.3. 回路定数設計

### 3.3.1. 変圧器漏れインダクタンスの設計

DAB コンバータでは、デッドタイム期間中にスナバキャパシタ  $C_8$  を  $L_8$  の磁気エネルギーにより充放電を行うことで ZVS 動作が達成でき、スイッチング損失の低減が期待できる。一方で、DAB コンバータでは入出力の直流電圧が一致しない場合、無効電流が増加し、半導体の電流最大値は大きくなる。高圧 DC/DC 変換器では、前述のように入出力電圧が等しい関係であるが、 実運転時に発生する電圧変動によりこの入出力電圧が一致しない場合での動作が想定される $^{(8)}$ 。これらのことを考慮して、本章では、 $L_8$  を 25% としている。

#### 3.3.2. スナバキャパシタの設計

ZVS 動作を達成するためには、デッドタイム期間中に  $L_S$  の磁気エネルギーによって充放電可能な  $C_S$  容量とする必要がある。一般的は、次式で示す関係を満足することで、ZVS 動作が可能であることが知られている $^{(4)}$ 。

$$I_{\min} = \frac{2V_{\rm DC}}{Z_0}$$

,  $Z_0 = \sqrt{\frac{L_{\rm S}}{C_{\rm S}}}$  (3.4)

ただし、 $I_{min}$ は ZVS 動作可能領域における最少電流である。ここで、(3.4)式を下記式のように変形することで ZVS 可能な  $C_S$  の容量を得ることができる。

$$C_{\rm S} \le \frac{1}{4} \left( \frac{I_{\rm min}}{V_{\rm DC}} \right)^2 \times L_{\rm S} \tag{3.5}$$

$C_S$  容量が大きくなるほど、半導体の両端電圧の dv/dt が緩やかになり、ターンオフ損失の低減につながるが、デッドタイム期間中に充放電動作が完了せず損失が増大する。ここで、セルの入出力電圧が等しいことを考慮すると  $L_S$  の電流  $I_{LS}$  は下記式で求めることができる。

$$I_{\rm Ls} = \frac{1}{2} \cdot \frac{V_{\rm Uin} + V_{\rm Cnm}}{\omega L_{\rm S}} \theta \tag{3.6}$$

先にも述べたが、洋上風力発電の設備利用率は30%程度である<sup>(3)</sup>ことを考慮すると、0.3p.u. 送電まで ZVS 可能であれば最も合理的に送電システム全体の損失を低減することができる。したがって、(3.6)式において、(0.3p.u.を送電する際の $\theta$ を代入して $I_{min}$ を求め、これを(3.5)式に代入することで、 $C_S$ の容量を設計している。

## 3.4. シミュレーション検証

#### 3.4.1. セル動作のシミュレーション検証

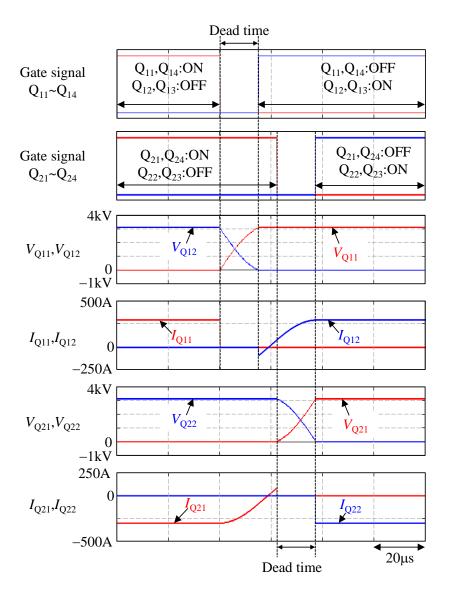

前述したように、本章では  $C_S$  の容量は 0.3p.u.送電時においても ZVS 動作が達成できるように設定する。そこで、図 3.4 に示す回路のシミュレーションを実施し、0.3p.u.送電時に ZVS 動作可能かの検証を行う。表 3.1 にシミュレーションを行うセルの回路定数を示す。シミュレーションでは、変圧器の巻線損失を模擬する抵抗 r を直列に接続し、1 次側および 2 次側それぞれに等分に配置し、 $C_S$  は(3.5)式および(3.6)式から 0.55μF に設定した。また、各セル入出力の直流キャパシタ  $C_{dc}$  は単位静電定数が 20ms となるように決定した。なお、単位静電定数とは、直流キャパシタの蓄積エネルギーを定格容量で規格化したものである( $^{(8)}$ )。図 3.8 に  $Q_{11} \sim Q_{14}$  および  $Q_{21} \sim Q_{24}$  のゲート信号、 $Q_{11}$  および  $Q_{12}$  の電圧  $V_{Q11}$  、 $V_{Q12}$ 、電流  $I_{Q11}$  、 $I_{Q12}$  と  $I_{Q21}$  の電圧  $I_{Q21}$  の電圧  $I_{Q21}$  の電圧  $I_{Q22}$  のシミュレーション波形を示す。

図 3.8 に示すように、1 次側および 2 次側でデッドタイム期間中に  $C_s$  の充放電動作が完了しており、ZVS 動作が達成できていることが確認できる。以上から、(3.5)式により  $C_s$  を決定することで、0.3p.u.送電時の ZVS が可能であり、合理的に送電システム全体の損失を低減することができる。

| Item                                           | Symbol        | Value                |

|------------------------------------------------|---------------|----------------------|

| Input voltage                                  | $V_{ m in}$   | 3.125kV              |

| Output voltage                                 | $V_{ m out}$  | 3.125kV              |

| Rated power                                    | $P_{ m cell}$ | 3.0MW                |

| Switching frequency                            | $f_{ m sw}$   | 500Hz                |

| Snubber capacitor                              | $C_{ m S}$    | 0.55μF               |

| Dead time                                      | $T_{ m d}$    | 15µs                 |

| Transformer turn ratio                         |               | 1:1                  |

| Transformer leakage inductance                 | 1             | 25%                  |

| (on a single-phase 3.125kV, 3.0MW, 500Hz base) | $L_{ m S}$    | $(260 \mu H)$        |

| Inner resistance of transformer                | r             | $5 \mathrm{m}\Omega$ |

| DC capacitor                                   | $C_{ m dc}$   | 10mF                 |

表 3.1 シミュレーションにおけるセルの回路定数

図 3.8 セルにおけるスイッチング動作に着目したシミュレーション波形

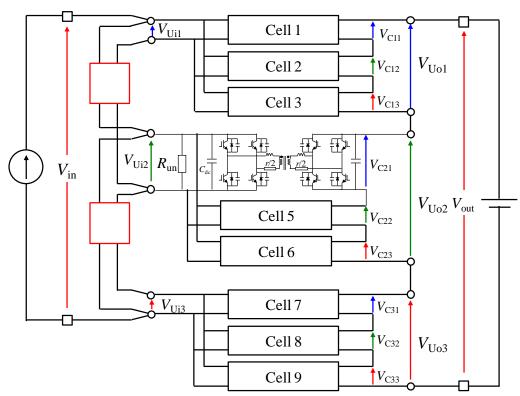

#### 3.4.2. 電圧バランス制御のシミュレーション回路

図 3.9 にシミュレーション回路を示し、表 3.2 にシミュレーション回路定数を示す。本シミュレーションは、基本動作および電圧制御の検証を目的として行うものであるため、セルおよびユニットの数を 3 としている。また、ユニットの数が 3 であるため補助変換器の必要台数は 2 台となる。実際の運用ではより多くのセルおよびユニット数を想定しており、MVDC および HVDC の電圧値と容量によりユニット数 n とユニット内のセル数 m を決定する。なお、図 3.9 中の  $R_{\rm un}$  は各ユニット間の損失バラつきを模擬した抵抗であり、(3.2)式に前述の変換効率 $\eta$ =96.65%で全損失に対する導通損失の割合  $r_{\rm sw}$ =56.42%、半導体損失のバラつき a=±30%を代入して求めたユニット間の送電電力のバラつき $\Delta P_{\rm Unit}$ =102.1kW が生じるように 95 $\Omega$ に設定した。補助変換器は $\Delta P_{\rm Unit}$  をゼロにするように機能するので、変換器容量

は $\Delta P_{\text{Unit}}$ の半分である 51.05kW となる。なお、HVDC 電圧は後段につながる陸上の DC/AC が制御していると仮定し、直流電圧源で模擬している。また、風車の発電電力は、前段の集電用 DC/DC 変換器でそれぞれ制御されているため、シミュレーション回路では電流源で模擬している。

図3.9 電圧バランス制御の検証におけるシミュレーション回路

| Conditions         | Symbol            | Value    |

|--------------------|-------------------|----------|

| Number of unit     | n                 | 3        |

| Number of cell     | m                 | 3        |

| Input voltage      | $V_{ m in}$       | 9.375kV  |

| Output voltage     | $V_{ m out}$      | 28.125kV |

| Rated power        | P                 | 27MW     |

| Unbalance resistor | $R_{\mathrm{un}}$ | 95Ω      |

表 3.2. シミュレーション回路の回路定数

## 3.4.3. 電圧バランス制御のシミュレーション結果

本章で実施するシミュレーションでは、洋上の風車は定格電力を発電しており、洋上で発電された電力を陸上に送電している場合を想定している。このとき、ユニット 2 の入力に  $R_{um}$ を接続し、他のユニットに比べてユニット 2 の損失が大きくなると仮定してシミュレーションを実施した。また、6kV 油入り変圧器の規格(10)において、 $L_S$  のバラつき範囲は $\pm 7.5\%$  と定められていることから、ユニット 2 およびユニット 3 の  $L_S$  が+7.5%、ユニット 1 の  $L_S$  を-7.5% と設定してシミュレーションを実施した。

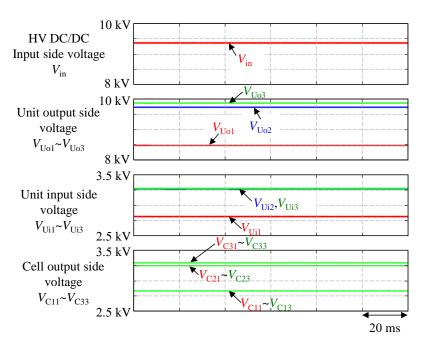

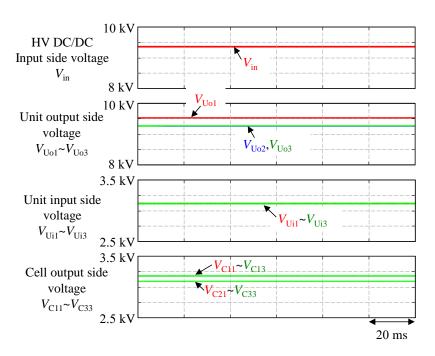

図 3.10 および表 3.3 にシミュレーション結果を示す。図 3.10 において、上から高圧 DC/DC 変換器の入力電圧  $V_{\rm in}$ 、各ユニットの出力電圧  $V_{\rm UO1} \sim V_{\rm UO3}$ 、各ユニットの入力電圧  $V_{\rm Ui} \sim V_{\rm Ui3}$ 、各セルの出力電圧  $V_{\rm Cii} \sim V_{\rm Cii3}$ である。また、図 3.10(a)に、バランス制御がなく  $V_{\rm in}$ のみ一定に制御している場合を示し、図 3.10(b)に、バランス制御を付加した場合を示す。バランス制御がある場合、ない場合にかかわらず  $V_{\rm in}$  は高圧 DC/DC 変換器により指令値  $V_{\rm in}$ \*=9.375kV一定に制御されている。また、図 3.10 からユニット 2 に  $R_{\rm in}$  が接続されおり、 $L_{\rm S}$  が+7.5%になっているため  $V_{\rm C2i} \sim V_{\rm C23}$  が最も小さくなっていることが確認できる。ここでバランス制御がある場合と無い場合の結果を比較する。表 3.3 に示すように、バランス制御がない場合、セル出力電圧の内、最大と最小の差は 461V であり、セル 1~3 の出力電圧の平均値に対するばらつきが最も大きく 9.34%である。同様に、ユニット入力側のバラつきは 9.73%である。一方で、バランス制御がある場合、最も大きいセル出力電圧の平均値に対するバラつきは 1.86%であり、ユニット入力電圧は完全にバランスしていることが確認できる。以上から、電圧バランス制御によりバラつきがわずかな範囲に抑制されている。以上から、本章で提案した電圧バランス制御を適用することで高圧 DC/DC 変換器が良好に動作すると結論付けられる。

(a) バランス制御がない場合のシミュレーション結果

(b) バランス制御がある場合のシミュレーション結果 図 3.10 電圧バランス制御のシミュレーション結果

| Conditions                  | Symbol                         | Fig. 3.10(a) | Fig. 3.10(b) |

|-----------------------------|--------------------------------|--------------|--------------|

| HV DC/DC input side voltage | $V_{ m in}$                    | 9.375kV      | 9.375kV      |

|                             | $V_{ m Uo1}$                   | 8.498kV      | 9.549kV      |

| Unit output side voltage    | $V_{ m Uo2}$                   | 9.744kV      | 9.286kV      |

|                             | $V_{ m Uo3}$                   | 9.882kV      | 9.288kV      |

|                             | $V_{ m Ui1}$                   | 2.821kV      | 3.125kV      |

| Unit input side voltage     | $V_{ m Ui2}$                   | 3.273kV      | 3.125kV      |

|                             | $V_{ m Ui3}$                   | 3.280kV      | 3.125kV      |

|                             | $V_{\rm C11} \sim V_{\rm C13}$ | 2.833kV      | 3.183kV      |

| Cell output side voltage    | $V_{\rm C21} \sim V_{\rm C23}$ | 3.248kV      | 3.096kV      |

|                             | $V_{\rm C31} \sim V_{\rm C33}$ | 3.294kV      | 3.096kV      |

表 3.3. シミュレーション結果

## 3.5. 実験結果

提案する電圧バランス制御について、検証を行うための3セル×3ユニット構成のミニモモデルを構築した。表 3.4 にミニモデルの回路定数を示し図 3.11 にミニモデルの回路構成を示す。なお、ミニモデルにおける直流キャパシタ  $C_{dc}$  は時容量が実機等同等になるようにを決定しており、インダクタンス  $L_S$  は、実機と同等のパーセントインピーダンスが得られるように変圧器の漏れインダクタンスに加えて追加でインダクタンスを接続している。

| 記号                                                | 値                                                                                                                                |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| P                                                 | 562.5W                                                                                                                           |

| $V_{ m in}$                                       | 75V                                                                                                                              |

| $V_{ m out}$                                      | 225V                                                                                                                             |

| n                                                 | 3                                                                                                                                |

| m                                                 | 3                                                                                                                                |

| $P_{ m cell}$                                     | 62.5W                                                                                                                            |

| $V_{\mathrm{Ui}1}{	extsf{	iny }}V_{\mathrm{Ui}3}$ | 25V                                                                                                                              |

| $V_{c11}$ ~ $V_{c33}$                             | 25V                                                                                                                              |

| $f_{ m sw}$                                       | 500Hz                                                                                                                            |

| $C_{ m dc}$                                       | 4.4mF                                                                                                                            |

| インダクタンス Ls                                        |                                                                                                                                  |

| LS                                                | (796µH)                                                                                                                          |

|                                                   | $P$ $V_{\rm in}$ $V_{\rm out}$ $n$ $m$ $P_{\rm cell}$ $V_{\rm Ui1} \sim V_{\rm Ui3}$ $V_{\rm c11} \sim V_{\rm c33}$ $f_{\rm sw}$ |

表 3.4. ミニモデルの回路乗数

図 3.11 ミニモデルの回路構成

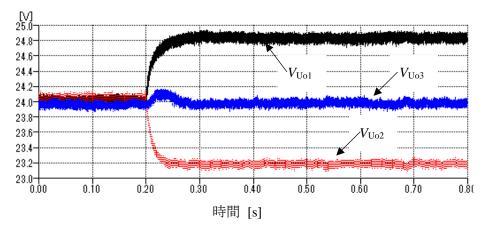

## 3.5.1. ユニット出力電圧バランス制御の確認

ユニット出力電圧バランス制御を確認する実験では、定常時の電圧バランスの確認に加えて、ユニット電圧バランス制御の制御指令値に外乱ステップを入力し、制御応答の確認も行った。なお、外乱ステップにより出力電圧  $V_{\rm out}$  に影響を及ぼさないようにユニット 1 には +2% の外乱ステップを与え、ユニット 2 には-2% の外乱ステップを与えた。

実験結果を図 3.12 に実験結果を示す。ここで、図 3.12 では各ユニット電圧として、各セル電圧の合計値をセル数 3 で除算したユニットごとにセル電圧平均値として表示している。 実験波形より外乱ステップを入力する 0.2s 以前では  $V_{Uol} \sim V_{Uo3}$  はバランスしておりほぼ一致していることが確認できる。 さらに 0.2s 以降は、指令値に追従し  $V_{Uol} \sim V_{Uo3}$  が変化していることが確認できる。

図 3.12 ユニット出力電圧バランス制御の実験結果

図 3.13 セル電圧バランス制御の実験結果

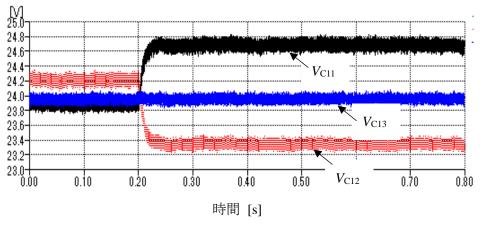

#### 3.5.2. セル電圧バランス制御の確認

セル電圧バランス制御を確認する実験では、ユニット出力電圧バランス制御の実験と同様に定常時の電圧バランスの確認に加えて、セル電圧バランス制御の制御指令値に外乱ステップを入力し、制御応答の確認も行った。なお、外乱ステップにより出力電圧  $V_{\rm out}$  に影響を及ぼさないように、ユニット 1 におけるセル 1 の電圧バランス制御指令値には+2%の外乱ステップを与え、セル 2 の電圧バランス制御指令値には-2%の外乱ステップを与えた。

実験結果を図 3.13 に実験結果を示す。図 3.13 にはセル  $1\sim9$  の内,最も電圧のばらつきが大きくなっていたユニット 1 におけるセル  $1\sim3$  の電圧  $V_{\rm CII}\sim V_{\rm CI3}$  を示している。実験波形より外乱ステップを入力した 0.2s 以前では, $V_{\rm CI2}$  が  $V_{\rm CI1}$  や  $V_{\rm CI3}$  に比べて  $0.2\sim0.3$ V 高い状態でセル電圧が各々バランスしていることが確認できる。 $V_{\rm CII}\sim V_{\rm CI3}$  が完全に一致しない理由については,図 3.5 に示したようにセル電圧のバラン制御は P 制御のみで実施しており,そのため定常偏差が残ることが原因である。さらに 0.2s 以降は,指令値に追従し  $V_{\rm CII}\sim V_{\rm CI3}$  が変化していることが確認できる。

図 3.14 ユニット入力電圧バランス制御の実験結果

### 3.5.3. ユニット入力電圧バランス制御の確認

ユニット入力電圧バランス制御を確認する実験では、ユニット出力電圧バランス制御やセル電圧バランス制御と同様に定常時の電圧バランスの確認に加えて、セル電圧バランス制御の制御指令値に外乱ステップを入力し、制御応答の確認も行った。なお、外乱ステップにより入力電圧  $V_{\rm in}$  に影響を及ぼさないように、ユニット 1 の制御指令値には+5%の乱ステップを与え、ユニット 2 およびユニット 3 の制御指令値には-2.5%の外乱ステップを与えた。

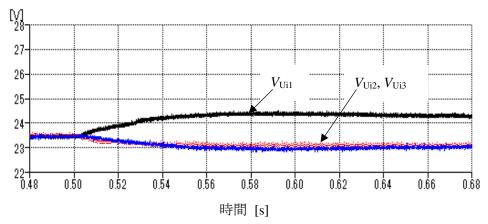

実験結果を図 3.14 に実験結果を示す。実験波形から、外乱ステップを入力した 0.5s 以前では、 $V_{Ui1} \sim V_{Ui3}$  は本論文で提案したバランス制御によりバランスしておりほぼ一致していることが確認できる。さらに 0.5s 以降は、指令値に追従し  $V_{Ui1} \sim V_{Ui3}$  が変化していることが確認できる。以上から、本論文で提案する電圧バランス制御の有効性が確認された。

#### 3.6. まとめ

本章では、高圧 DC/DC 変換器の回路構成として、DAB コンバータを多数直並列に接続した回路方式を提案し、各セル間の電圧バラつきを抑制する制御方式についての検討を行った。さらに、洋上風力発電の設備利用率は 30%程度であることを考慮し、送電システム全体の損失を合理的に低減できるように、0.3p.u.送電時に ZVS 動作可能なスナバキャパシタ容量に設計した。また、シミュレーション検証を実施し、 設計したスナバキャパシタの有効性を確認するとともに、提案する制御方式のシミュレーション検証およびミニモデルでの実験結果により有効性を確認した。以上により、高圧 DC/DC 変換器の実現可能性を示した。

# 参考文献

- (1) 小熊功太・フィルマン・サソンコ・萩原誠・赤木泰文: 「モジュラー・マルチレベル・カスケード変換器を用いた FTF(Front-to-Front)システムの実験検証」, 電学論 D, Vol.135, No.7, pp.794-801 (2015)

- (2) 長谷川泰三・別井孝司・大西修一・竹田正俊・瀬戸誠・村上昇太郎・光庵豊一:「系統 安定化用大容量自励式無効電力補償装置の開発」,電学論 D, Vol.111, No.10, pp.845-854 (1991)

- (3) R.W. De Doncker, M. Divan, and M.H. Kheraluwala: "A Three-Phase Soft-Switching High-Power-Density dc/dc Converter for High-Power Applications", IEEE Trans. on IA, Vol.27, No.1, pp.63-73 (1991)

- (4) M. H. Kheraluwala, R. W. Gascoigne, D. M. Divan, and E. D. Baumann: "Performance Characterization of a High-Power Dual Active Bridge DC-to-DC Converter", IEEE Trans. on IA, Vol. 28, No. 6, pp.1294-1301 (1992)

- (5) F. Sasongko, M. Hagiwara, H. Akagi: "A Front-to-Front (FTF) System Consisting of Multiple Modular Multilevel Cascade Converters for Offshore Wind Farms", Proc. of 2014 International Power Electronics Conference (IPEC-Hiroshima 2014-ECCE ASIA), pp.1761-1768 (2014)

- (6) 林祐輔・三野正人:「380V 直流給電システムにおける電源高出力密度化の一手法」,電 学論 D, Vol.132, No.8, pp.817-825 (2012)

- (7) 井上重徳・赤木泰文: 「次世代 3.3kV/6.6kV 電力変換システムのコア回路としての双方 向絶縁形 DC/DC コンバータ」, 電学論 D, Vol.126, No.3, pp.211-217 (2006)

- (8) 井上重徳・赤木泰文: 「双方向絶縁形 DC/DC コンバータの動作電圧と損失解析」,電学論 D, Vol.127, No.2, pp.189-197 (2007)

- (9) 北田亮平・赤木泰文:「複数台の双方向絶縁形 DC/DC コンバータを用いたマルチレベル・カスケード BTB システムの制御法」,電学論 D, Vol.130, No.12, pp.1307-1314 (2010)

- (10) 日本工業標準調査会:「JIS C 4304:2013 配電用 6kV 油入変圧器」, (2013)

## 第4章

# 高圧 DC/DC 変換器用変圧器の小型高効率化に向けた検討

高圧 DC/DC 変換器には、HVDCMVDC 間における電気的絶縁と高効率な電力変換が要求される。これを実現する方式として、DAB コンバータをセルとして多数直並列接続する DAB 方式を前章では検討した。しかし、DAB 方式は、多数の DAB コンバータにより構成されるという特徴から DAB コンバータと同数の変圧器が必要となり、システムの大型化が懸念される。本章では、高圧 DC/DC 変換器に小型高効率化を実現するために、変圧器の小型高効率化と半導体導通損の削減を目的に、2 直列 3 並列接続した半導体素子を適用し、変圧器数と、半導体素子導通損失の削減を検討する。また、第 3 章で言及した多重変圧器構造を採用し、変圧器鉄心の小型化を検討する。

#### 4.1. 2 直列 3 並列接続した半導体素子の適用

多数の DAB コンバータから構成される高圧 DC/DC 変換器では、DAB コンバータにおける半導体素子の耐圧から 1 セルあたりで出力可能な直流電圧が制約を受け、必要なセル数が決定する。したがって、2 直列接続した半導体素子を適用することで、1 セルあたりが出力する電圧を 2 倍に増加させることができ、必要なセル数を半減させることが可能になるため、変圧器数も半減しシステムの小型化が期待できる。しかし、直列に接続された半導体素子において、ゲート信号のバラツキや素子特性のバラツキなどに起因して発生する直列素子間の電圧のアンバランスが課題となる(1)-(5)。

一方で、半導体素子の導通損失低減には、並列接続によって、1素子当たりの電流を低減することが有効である。しかし、半導体素子の並列接続についても電流経路のインピーダンスのばらつきや素子特性のばらつきに起因する電流アンバランスによって損失集中が課題となる<sup>(6)-(8)</sup>。以下では、半導体素子の直列接続および並列接続に関する先行研究を紹介しつつその課題について整理する。

#### 4.1.1. 半導体素子の直列接続に関する先行研究と課題

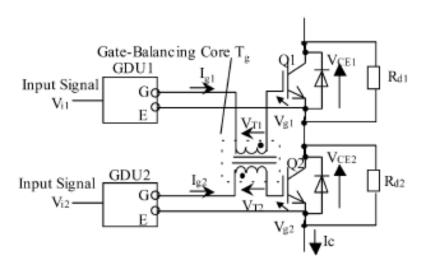

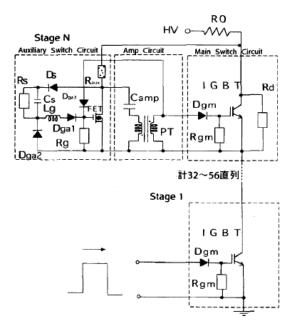

これまでに、半導体素子の直列接続を実現する方式として、いくつかの方式が検討されている(1)~(5)。 文献(1)では、図 4.1 に示すように、各 IGBT のゲート駆動回路のゲートリード線部分に共通のコアを挿入することで、各 IGBT の入力容量を充放電するゲート電流の経路を磁気的に結合するため、各ゲート電流が一致し、電圧アンバランスが抑制できるという方式が提案されている。

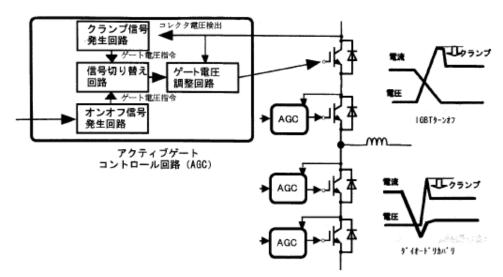

文献(2)では、図 4.2 に示すように、各 IGBT のコレクタ電圧を検出し、コレクタ電圧が高くなるほど該当する IGBT のゲート電圧が高くなるように制御するアクティブゲート制御

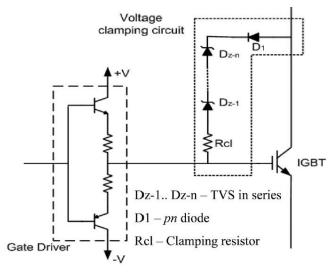

方式が提案されている。さらに、文献(3)では、各 IGBT に並列接続する RCD スナバ回路により電圧アンバランスの抑制を行いつつ、RCD スナバ回路での損失を抑制するために、直列接続した複数の TVS(Transient Voltage Suppressors)とダイオードおよび抵抗からなるクランプ回路をゲート・コレクタ間に追加するハイブリッド方式が議論されている。この方式では、RCD スナバ回路のスナバキャパシタを損失が最小化するように設定することで、損失の増加を抑制している。

図 4.1 ゲート駆動回路のゲートリード線部分に共通のコアを挿入する方式の構成例<sup>(1)</sup> (出典: K. Sasagawa, Y. Abe, and K. Matsuse: "Voltage-Balancing Method for IGBTs Connected in Series", *IEEE Trans. on Industry Applications*, Vol.40, No.4 pp. 1025-1030 (2004))

図 4.2 アクティブゲート制御方式の構成例(2)

(出典:加藤修治・上田茂太・酒井洋満・相澤英俊:「スナバレス IGBT 直列接続に適したアクティブゲートコントロール」,電学論 D, Vol. 122, No.8, pp.816-822 (2002))

文献(4)では、電圧アンバランスと素子の寄生パラメータの関係に着目し、DSP(Digital Single Processor)や FPGA(Field Programmable Gate Array)などの制御 IC を使用して、ゲート電圧にナノ秒オーダーの遅延を与えることで電圧アンバランスを抑制するディジタル回路を適用した方式が提案されている。文献(5)では、多数直列接続になった IGBT のうち最下段と第2直列段両者の導通による変位電流で全素子を導通させる「2段従属方式」が提案されている。しかし、この方式では、変位電流を各段に導くための回路が必要となることや、低電圧スイッチング時における、従属段の過電圧に課題があり、過電圧を防止するアクティブクランプ回路が別途必要になる。

図 4.3 ハイブリッド方式の構成例(3)

(出典: R. Withanage, and N. Shammas: "Series Connection of Insulated Gate Bipolar Transistors (IGBTs)", *IEEE Trans. on Power Electronics*, Vo.27, No.4, pp.2204-2212 (2012))

図 4.4 ディジタル回路を適用した方式の構成例(4)

(出典:神宮克哉・和田圭二:「ディジタル回路を適用した SiC-MOSFET 直列接続における電圧不平衡の改善法」,電学論 D, Vol.138, No.5, pp.417-427 (2018))

図 4.5 2 段従属方式の構成例(5)

(出典:鈴木昭弘・岩田明彦・寺本昭好・小関忠・中村典雄・神谷幸秀: 「50kV 2kA 従属駆動 IGBT スイッチング」, 電学論 D, Vol.121, No.3, pp.308-315 (2001))

このように、文献(1)~(5)で提案されている方式では、いずれの方式も、電圧センサやダイオードなどの追加の部品が必要となる。本学位論文で提案している高圧 DC/DC 変換器では、前述の通り、多数の DAB コンバータから構成しており、上記までの方式を適用した場合、膨大な数の追加部品が必要となり、コスト面および信頼性の観点から課題があるため、不向きである。

## 4.1.2. 半導体素子の並列接続に関する先行研究と課題

これまでに、半導体素子の並列接続を実現する方式についても、いくつかの方式が検討されている(<sup>೧),(8)</sup>。文献(7)では、図 4.6 に示すように、電流経路におけるインダクタンスを均等化することで、各半導体素子の電流を均一にしている。この方式では、電流センサなどの追加部品は必要ないため、コスト面などの課題はないが、半導体素子の特性バラつきについては考慮されていないため、これらが課題となり得る。文献(8)では、図 4.8 に示すように各半導体素子に流れる電流をゲート電圧によって制御するアクティブゲート制御が検討されている。この方式では、各 IGBT に流れる電流をセンシングし、電流の立上りまたは立下りエッジを一致させるようにタイムシフトしたゲート電圧を各半導体素子に入力する。さらに、個別にゲート電圧の大きさを制御することで、各半導体素子の電流バランスを達成することができる。しかし、本学位論文で提案する高圧 DC/DC 変換器にした場合、素子の直列接続と同様に、膨大な数の電流センサが必要となるためコスト面でも課題がある。

|                              | Design-A (Proposal) |                                               |                 |      |     | Design-B                                             |          |      |      |      | Design-C       |           |      |      |

|------------------------------|---------------------|-----------------------------------------------|-----------------|------|-----|------------------------------------------------------|----------|------|------|------|----------------|-----------|------|------|

| IGBT assembly                | Square              |                                               |                 |      |     | Square                                               |          |      |      |      | One row        |           |      |      |

|                              |                     | Wide lan                                      | ninated         |      |     |                                                      | T - type |      |      |      | Equ            | al length | bar  |      |

| Bus-bar<br>assembly          |                     | 2<br>10 0 N2<br>10 0 P2<br>10 0 N4<br>10 0 P4 | X<br>X<br>Capar |      |     | 1 2 X    N P   2 2   0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |          |      |      |      | Lamir<br>Bus-b |           |      | Y Y  |

| IGBT No.                     | 1 2                 | 3                                             | 4               | Ave. | 1   | 2                                                    | 3        | 4    | Ave. | 1    | 2              | 3         | 4    | Ave. |

| Inductance L [nH]            | 65.4 64.            | 2 65.6                                        | 64.2            | 64.9 | 102 | 96                                                   | 107      | 99   | 101  | 52.8 | 51.6           | 51.8      | 52.7 | 52.2 |

| Unbalance \( \Delta L[\%] \) | 0.8 -1.             | 0 1.2                                         | -1.0            |      | 1.0 | -5.0                                                 | 5.9      | -2.0 | _    | 1.1  | -1.2           | -0.8      | 0.9  | _    |

図 4.6 電流経路におけるインダクタンスを均等化する方式の構成例(7)

(出典:森和久・大沼直人・迫田友治・松本洋平・薮内達志:「超高速エレベータ用 IGBT 並列電力変換器」,電学論 D, Vol.137, No.1, pp.1-9 (2017))

図 4.6 アクティブゲート制御方式

(出典: D. Bortis, J. Biela, and J.W. Kolar: "Active Gate Control for Current Balancing of Parallel-Connected IGBT Modules in Solid-State Modulators," *IEEE Trans. on Plasma Science*, Vol.36, No.5, pp.2632-2637 (2008))

### 4.1.3. 本学位論文で提案する2直列3並列接続半導体素子の実現方法

前述の通り、従来方式により半導体素子の2直列接続を実現するには、多数の追加の部品が必要となるため、コストの観点から実用的でない。そこで、本章では、DAB コンバータにおける各半導体素子に並列に接続されるスナバキャパシタを活用する方式を提案する。具体的には後述するが、スナバキャパシタの働きにより、半導体素子のターンオフ時における dv/dt を緩やかにすることで、電圧アンバランスを抑制する。さらにターンオン時においては DAB コンバータ特有の ZVS 動作を達成することでターンオン時の電圧はゼロとなるため、電圧アンバランスは発生しない。3並列接続についても、同様に、追加の部品を必要とするアクティブゲート制御方式ではなく、図 4.6 に示すような受動的な方式によって実現することを検討する。しかし、図 4.6 に示す方式では、半導体素子の特性バラつきについては考慮されていないため、これらのバラつきの影響についてもスイッチング試験を行うことで検証する。

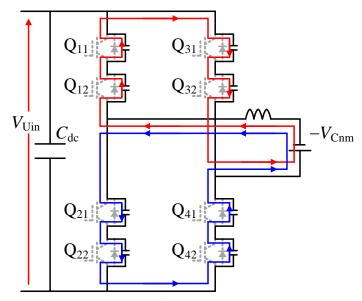

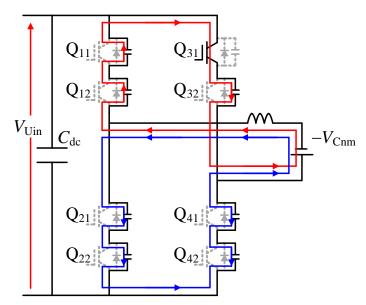

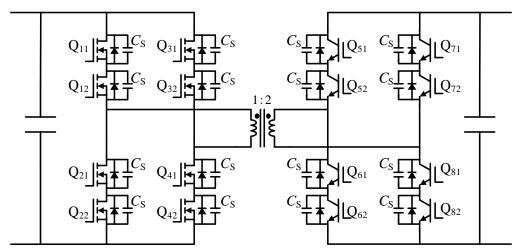

#### 4.2. ZVS 動作を利用した半導体素子の直列接続

図 4.7 に 2 直列接続した半導体素子を適用した場合におけるセルの回路構成を示す。ZVS 動作が達成されない場合,各素子に接続されるスナバキャパシタは素子がターンオンすると短絡されるため(スナバ短絡),蓄えられた静電エネルギーがすべて素子で損失されてしまう。したがって,本学位論文で提案する方式では,スナバキャパシタは,ターンオフ時の電圧アンバランス抑制と ZVS 動作を両立する値に設計する必要がある。

図 4.7 2 直列接続した半導体素子を適用した場合におけるセルの回路構成

#### 4.3. スナバキャパシタ容量の設計

#### 4.3.1. ZVS 動作による容量の制限

ZVS 動作の実現には、デッドタイム期間中にスナバキャパシタの充放電動作を完了しなければならないが、送電電力が小さくなるほど充放電動作には時間を要する。ここで、スナバキャパシタの容量と ZVS 動作について考える。 $V_{\text{Uin}}=V_{\text{Cnm}}$  であるため各 IGBT がターンオフする瞬間の電流  $I_{\text{off}}$  は下記式で求められる。

$$I_{\text{off}} = \frac{V_{\text{Uin}} + V_{\text{Cnm}}}{2\omega L_{\text{S}}} \theta \tag{4.1}$$

ただし、(4.1)式において、 $\omega$ = $2\pi f_{sw}$ で、 $f_{sw}$ はスイッチング周波数であり、IGBT や接続導体、変圧器で発生する損失は考慮していない。また、 $\theta$ は変圧器に印加される 1 次側および 2 次側の矩形波電圧の位相差であり、下記の式で求めることができる。

$$\theta = \frac{\pi}{2} - \sqrt{\left(\frac{\pi}{2}\right)^2 - \frac{\pi \alpha L_{\rm S} P}{V_{\rm Uin} V_{\rm Cnm}}} \tag{4.2}$$

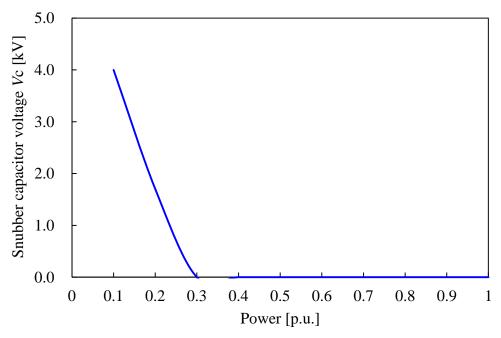

ただし、(4.2)式において P はセルの送電電力である。図 4.8 に 1 次側におけるデッドタイム期間中の回路動作を示す。ただし、図 4.8 において、2 次側は、直流電源  $V_{\rm Cnm}$  で等価的に示している。デッドタイム期間中は、(4.1)式および(4.2)式で求められる電流  $I_{\rm off}$  が各 IGBT に接続されるスナバキャパシタを充放電することで ZVS 動作を行う。また、図 4.8 に示すように、デッドタイム期間中には上アームと下アームにそれぞれ等しく分流するため、ZVS 動作が実現できなかった場合にスナバキャパシタに残留する電圧  $V_{\rm C}$  は下記式で求めることが知られている $^{(9)}$ 。

$$V_{\rm C} = V_{\rm Uin} - \frac{I_{\rm off}}{2} \sqrt{\frac{L_{\rm S}}{C_{\rm S}}} \sin\left(\sqrt{\frac{1}{L_{\rm S}C_{\rm S}}}\right) T_{\rm d} \tag{4.3}$$

ただし、(4.3)式において  $T_d$  はデッドタイムであり、 $C_S$  は 2 直列時の合成容量である。スナバキャパシタに電圧が残留している状態で IGBT がターンオンすると、スナバ短絡が発生し損失となる。このとき、スナバキャパシタに蓄えられているすべての静電エネルギーが IGBT で消費されることに加えて、対向アームのスナバキャパシタがターンオンした IGBT を介して充電されることで損失が発生することから、スナバ短絡による損失  $E_{on}$ (ターンオン損失)は下記式のようになる。

$$E_{\rm on} = \frac{1}{2} C_{\rm S} V_{\rm C}^2 \times 2 = C_{\rm S} V_{\rm C}^2 \tag{4.4}$$

ZVS 動作の実現のためには, (4.4)式で求められる損失がゼロとなるような容量に設計する必要がある。

図 4.8 1次側におけるデッドタイム期間中の回路動作

図 4.9 ゲート電圧のバラツキにより  $Q_{31}$  のターンオフが遅延した場合におけるデッドタイム期間中の回路動作

## 4.3.2. 電圧アンバランスによる容量の制限

前述のように、2S3P-IGBT の適用のためには、ゲート電圧のバラつきに起因する電圧アンバランスをスナバキャパシタの設計により抑制する必要がある。図 4.9 にゲート電圧のバラツキにより  $Q_{31}$  のターンオフが遅延した場合におけるデッドタイム期間中の回路動作を示す。図 4.8 では、すべての IGBT のスイッチング動作にバラツキがないため、上アームと下アームに分かれた電流経路のインピーダンス(スナバキャパシタの合成容量)は等しく、電流は均等に分流しているが、図 4.9 に示すように 1 つの IGBT のターンオフが遅延した場合、電

流経路のインピーダンスは等しくならないため、均等に分流しない。上アームと下アームの 電流は、それぞれの経路のインピーダンスの比で求めることができるため、上アームの電流 Ip は以下の式で求められる。

$$I_{p} = \frac{2}{3}I_{\text{off}} \tag{4.5}$$

先にターンオフした IGBT に並列に接続されているスナバキャパシタは, (4.5)式で求められる電流で充電され, 電圧アンバランス $\Delta V$  が発生する。したがって, (4.5)式から電圧アンバランス $\Delta V$  は下記式で求めることができる。

$$\Delta V = \frac{1}{2C_{\rm s}} \int_0^{\Delta T} I_{\rm p} dt = \frac{I_{\rm off}}{3C_{\rm s}} \Delta T \tag{4.6}$$

ただし、(4.6)式において $\Delta T$  はゲート電圧が下降開始するタイミングの不一致に伴うバラツキ時間である。このバラツキ時間は、ゲート駆動回路のフォトカプラ等で発生する伝達遅延時間のバラツキであり、本章では、500ns と仮定している。また、最終的には素子のディレーティングやシステム全体の仕様等により $\Delta V$  の許容値が決定するが、本論文では電圧アンバランスの範囲を $\pm 10\%$  として検討を行う。(4.6)式から確認できるように、電圧アンバランスはターンオフ時の電流に比例して増加することから、定格動作時が最も厳しい条件となる。このため、定格出力時に電圧アンバランスが $\pm 10\%$ 以下となるようにスナバキャパシタの設計を行う必要がある。

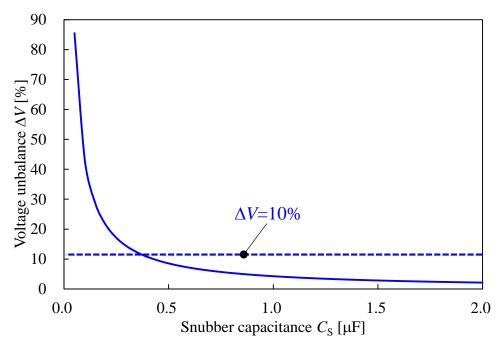

#### 4.3.3. スナバキャパシタの容量設計

表 4.1 にセルの回路定数を示す。現行の IGBT の定格電圧は  $6.5 \mathrm{kV}$  であり,直流電圧  $6.25 \mathrm{kV}$  に対して耐圧の余裕がないが,2 直列接続することで直流電圧が耐圧の半分程度となり,耐圧に対して十分な余裕を確保できる。また, $L_S$  については,第 3 章でも説明したように DAB コンバータが入出力の直流電圧が一致しない場合無効電流が増加し電流最大値が大きくなることを考慮して,25%としている。

図 4.10 に表 4.1 の回路定数から算出した定格送電時における電圧アンバランス $\Delta V$  とスナバキャパシタ  $C_S$  の関係を示す。なお,図 4.10 中の  $C_S$  は 2 直列接続時の合成容量を示している。図 4.10 に示すように, $C_S$  の容量に反比例して $\Delta V$  が減少しており, $C_S$ =0.5 $\mu$ F 以上で $\Delta V$  が目標値である $\pm$ 10%以下となっていることが確認できる。一方で, $C_S$  の容量が大きいほど ZVS 動作の達成は難しくなり,スナバ短絡による損失が増加してしまう。そこで,本論文では目標値 $\pm$ 10%に対して余裕をもたせ,幅広い動作領域で ZVS 動作を達成するために  $C_S$ =0.5 $\mu$ F とした。

図 4.11 に(4.1)~(4.3)式により求めた各送電電力のスナバキャパシタの残留電圧  $V_{\rm C}$  を示す。図 4.11 に示すように  $C_{\rm S}$ =0.5 $\mu F$  に設定した場合 0.3 $\mu F$  の動作領域で ZVS 動作が達成できることが確認できる。

| 表 4.1.  | セルの回路定数 |

|---------|---------|

| 1X T.1. |         |

| Item                                           | Symbol              | Value           |

|------------------------------------------------|---------------------|-----------------|

| Input voltage                                  | $V_{ m Uin}$        | 6.25kV          |

| Output voltage                                 | $V_{ m Cnm}$        | 6.25kV          |

| Rated power                                    | $P_{\mathrm{cell}}$ | 8.93MW          |

| Switching frequency                            | $f_{ m sw}$         | 500Hz           |

| Snubber capacitor                              | $C_{\mathrm{S}}$    | 0.5μF           |

| Dead time                                      | $T_{ m d}$          | 15µs            |

| Transformer turn ratio                         |                     | 1:1             |

| Transformer leakage inductance                 | Ls                  | 25%             |

| (on a single-phase 6.25kV, 8.93MW, 500Hz base) | LS                  | $(423.5 \mu H)$ |

| DC capacitor                                   | $C_{ m dc}$         | 10mF            |

図 4.10 スナバキャパシタ容量と電圧アンバランス AV の関係

図 4.11 スナバキャパシタ容量と残留電圧 Vcの関係

## 4.3.4. シミュレーション結果

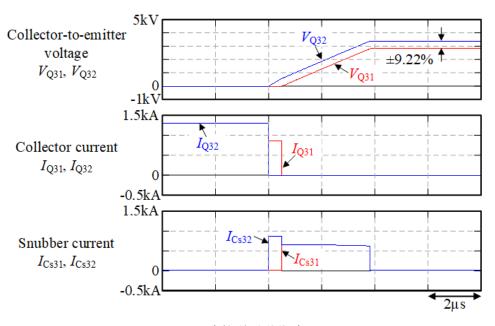

図 4.12 に  $C_{S=}0.5$ μに設定した際の定格送電時(電圧アンバランス確認)およびに 40%送電時 (ZVS 動作確認)における  $Q_{31}$  および  $Q_{32}$  のコレクタ・エミッタ間電圧  $V_{O31}$ ,  $V_{O32}$  とコレクタ 電流  $I_{\mathrm{O31}},~I_{\mathrm{O32}}$ とスナバキャパシタ  $C_{\mathrm{S31}}$ および  $C_{\mathrm{S32}}$ の充放電電流  $I_{\mathrm{CS31}},~I_{\mathrm{CS32}}$ のシミュレーシ ョン波形をそれぞれ示す。なお、シミュレーションでは、ゲート駆動回路のフォトカプラで 発生する伝達遅延ばらつきを模擬して、 $Q_{31}$ のゲート信号を他の IGBT に比べて 500ns 遅延 させて行い、定格動作時では IGBT のターンオフに着目し、40%送電時には IGBT のターン オンに着目している。図 4.12(a)に示すように、定格運転時に  $Q_{31}$  のゲート信号が 500ns 遅延 すると、先にターンオフした $Q_{32}$ に接続されるスナバキャパシタ $C_{832}$ が充電されるため、 $V_{Q32}$ は先に増加し始める。500ns 経過後は  $Q_{31}$  がターンオフし, $C_{S31}$  が充電され  $V_{O31}$  が増加する。 このとき、 $C_{S32}$ は先に $\Delta V$ だけ充電されているため、電圧アンバランス $\Delta V$ が発生する。シミュ レーション結果より発生している電圧アンバランスは±9.22%であり,目標値である±10%以下 に収まっていることが確認できる。 さらに, 図 4.12(b)に示すように 40% 送電時では, 図 4.12(a) と同様に Q31 のターンオンが他の IGBT に比べて 500ns 遅延しているが、対向するアームの  ${f Q}_{41}$  および  ${f Q}_{42}$  がターンオフするため,図  ${f 4.8}$  に示す経路の電流経路が形成される。したがっ て、 $C_{S31}$  および  $C_{S32}$  はともに放電を開始し、電圧がゼロになるとダイオードに転流する。こ こで、図 4.12(b)から  $Q_{31}$  のダイオードが先に導通していることが確認できる。これは、 $Q_{31}$  の ターンオフが 500ns 遅延していたため放電を開始する直前の電圧は  $V_{O32}>V_{O31}$  の関係であり,  $C_{S32}$  の放電のほうが  $C_{S31}$  に比べて時間を要したことが原因である。その後、 $V_{O32}$  もゼロにな ると Q<sub>32</sub> のダイオードに転流し、電流極性が反転すると既にオンしている Q<sub>31</sub> および Q<sub>32</sub> の IGBT に転流する。したがって、前述のように ZVS 動作を実現することでターンオン動作に ばらつきが発生しても電圧アンバランスは発生しない。以上から、スナバキャパシタを図 4.10 により決定した容量とすることで定格動作時に電圧アンバランス±10%以下の達成と 30%送 電時の ZVS 動作実現を両立させることができる。

(b) 軽負荷運転動作時(30%送電) 図 4.12 シミュレーション結果

#### 4.4. スイッチング試験

#### 4.4.1. 接続導体設計

前述のように直列接続した IGBT の電圧アンバランスは、スナバキャパシタの設計により抑制する。一方で、大電流化のために IGBT を多数並列接続する場合に、電流アンバランスが発生してしまうと、損失が一部の素子に集中してしまい、温度上昇幅が大きくなるため IGBT の寿命の低下につながる(๑-(๑)。また、本論文で提案するような大容量の変換器に使用する高耐圧の IGBT モジュールは lin1 モジュールであり、1 モジュールのサイズは 140mm×190mm と大きいため、接続導体が大きくなってしまい、配線インダクタンスの増加が懸念される。配線インダクタンスは、ターンオフ損失の増加につながることから可能な限り小さいことが望まれる(¹o)。そこで、本論文では、接続導体を積層導体とすることで、配線インダクタンスの増加を抑制している。

電流アンバランスの要因としては、以下の要因があげられる(10)。

- (1) 電流経路の配線インピーダンスのバラつき

- (2) 並列素子間の I-V 特性のバラつき

- (3) 並列素子間のゲート閾値電圧のバラつきに伴うスイッチング不一致

(1)および(2)については、素子オン状態における定常定期な電流アンバランスの要因となり、(3)はスイッチング時の過渡的な電流アンバランスを引き起こす。これに対して、文献(23)では、パルス電源用に多数並列接続した IGBT の電流アンバランスを抑制するアクティブゲート制御が提案されている。この方式では、各 IGBT に流れる電流をセンシングし、電流の立上りまたは立下りエッジを一致させるようにタイムシフトしたゲート電圧を各 IGBT に入力する。さらに、個別にゲート電圧の大きさを制御することで、各 IGBT の電流バランスを達成することができる。しかし、各素子に対して電流センサが必要になるため、本論文で提案するシステムに適用した場合、膨大な数の電流センサが必要となり現実的ではないため、本論文では、各 IGBT への電流経路における配線インピーダンスの均一化と選別による並列接続素子の組み合わせにて電流アンバランスの抑制を行った。具体的には、接続導体の設計において、上アームと下アームの接続箇所(AC 端子)を 3 端子構造とし、各端子位置をそれぞれのIGBT の中心に配置している。また、両端の IGBT は、中心に配置した IGBT 基準で左右対称の位置に配置しており、接続導体も左右対称な構造としている。

図 4.13 に設計した接続導体を適用したスイッチング試験回路の構成を示す。図 4.13 に示す接続導体は 1 レグ分であり、直流キャパシタ  $C_{dc}$  をはさんで反対側に同じ接続導体を配置することで 2 レグ分構成できる。また、図 4.13 の接続導体における電磁界解析ソフトを用いた検証の結果、 $C_{dc}-Q_{11}-Q_{12}-Q_{21}-Q_{22}-C_{dc}$  の経路における配線インダクタンスは 75nH である。さらに、並列接続している各 IGBT に対する電流経路のインピーダンスの内で最も小さくなるのは、中心に配置した IGBT への経路であり、両端の IGBT への経路に比べて 1.93%小さくなった。事前の選別により IGBT の特性が等しい場合、電流アンバランスは経路のインピーダンスのバラつきに依存するが、本論文では、1.93%とわずかなバラつきに抑制できて

図 4.13 設計した接続導体

いるため、インピーダンスのバラつきが電流アンバランスに与える影響は小さくなっている。

#### 4.4.2. スイッチング試験

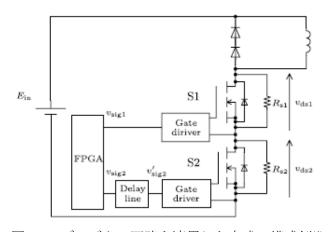

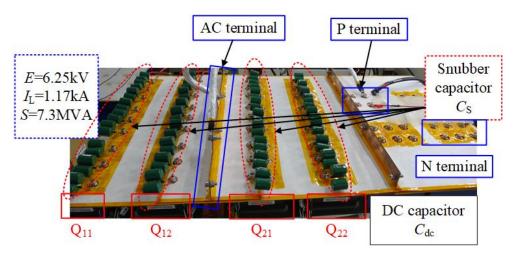

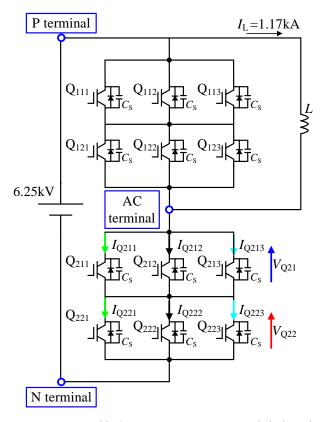

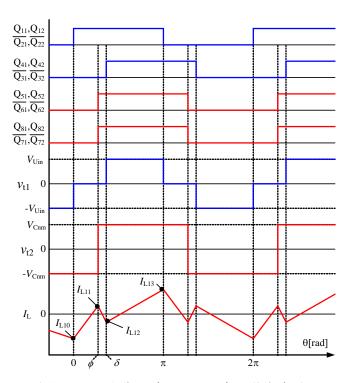

図 4.14 にスイッチング試験回路の構成を示す。試験では、下アームの上側素子  $Q_{211} \sim Q_{213}$  および下側素子  $Q_{221} \sim Q_{223}$  にゲート信号を与えており、下側素子  $Q_{221} \sim Q_{223}$  のゲート信号は 500ns 遅延させ、上アームは常時オフとしている。

ここで、本学位論文で提案している高圧 DC/DC 変換器には、現状の半導体モジュールで最も大容量な 6.5kV/1000A の Si-IGBT(CM1000HG-130XA)の適用を想定している。しかし、この IGBT モジュールは開発されたばかりであり入手が難しいため、同耐圧の CM750HG-130R(6.5kV/750A)で代用する。したがって、以下に示す通りに、実機の動作条件を今回使用する IGBT モジュール用に換算する必要がある。

定格電流=750A×3 並列×

$$\frac{1565A}{3000A}$$

=1173.75A (4.7)

さらに、スナバキャパシタ容量  $C_{\rm S}$  (2S 相当)は全電力(8.93MW)に対する蓄積エネルギーの比率が等しくなるよう以下の式により算出した。

$$C_{\rm S} = \left(\frac{6250 \text{V}}{6250 \text{V}}\right)^2 \times \left(\frac{6250 \text{V} \times 1173.75 \text{A}}{8.93 \text{MW}}\right) \times 0.5 \mu \text{F} = 0.375 \mu \text{F}$$

(4.8)

図 4.14 の実験回路では,インダクタ L の電流  $I_L$  が(4.7)式に示す換算後のセルの定格電流である 1.17kA になるようにパルスのオン時間を調整しており各アームにおける合成容量が(4.8)式で示す換算後の合成容量 0.375 $\mu$ F になるように各 IGBT モジュールには  $0.25\mu$ F のスナバキャパシタ  $C_S$  を接続している。本論文でのスイッチング試験では,下アームでは IGBT のみが導通し,上アームではダイオードのみが導通する。

表 4.2 にスイッチング試験における IGBT の組み合わせを示す。ペア A は、配線インピー

ダンスが小さくなる中心の素子( $Q_{212}$ および  $Q_{222}$ )の  $V_{ce(sat)}$ が小さい組み合わせであり、特に下側素子で飽和電圧  $V_{ce(sat)}$ とゲート閾値電圧  $V_{ge(th)}$ の差が大きい組み合わせである。一方で、ペア B は、各 IGBT  $V_{ce(sat)}$ と  $V_{ge(th)}$ の差が小さくなるように選別した組み合わせである。なお、本論文において素子の選別・組み合わせは、IGBT モジュールの出荷試験データを使用して行っており、別途使用前に特性取得用の試験は実施していない。

図 4.14 2S3P 接続 IGBT のスイッチング試験回路

| 表 4.2 | Q <sub>211</sub> ~Q <sub>223</sub> のオン | ´電圧 $V_{ce(sat)}$ およびケ | ート閾値電圧 $V_{ m gs(th)}$ |

|-------|----------------------------------------|------------------------|------------------------|

|       |                                        |                        |                        |

|             |                  | ( ,                  |                  |                      |                 |

|-------------|------------------|----------------------|------------------|----------------------|-----------------|

| IGBT        |                  | Pair A<br>(図 4.15)   |                  | Pair B<br>(図 4.16)   |                 |

|             |                  | $V_{\text{ce(sat)}}$ | $V_{\rm ge(th)}$ | $V_{\text{ce(sat)}}$ | $V_{ m ge(th)}$ |

| Top side    | $Q_{211}$        | 4.23V                | 6.23V            | 4.13V                | 6.23V           |

|             | Q <sub>212</sub> | 4.13V                | 6.23V            | 4.12V                | 6.18V           |

|             | Q <sub>213</sub> | 4.23V                | 6.22V            | 4.14V                | 6.20V           |

| Bottom side | Q <sub>221</sub> | 4.45V                | 6.31V            | 4.16V                | 6.21V           |

|             | Q <sub>222</sub> | 4.12V                | 6.18V            | 4.16V                | 6.22V           |

|             | $Q_{223}$        | 4.44V                | 6.33V            | 4.17V                | 6.22V           |

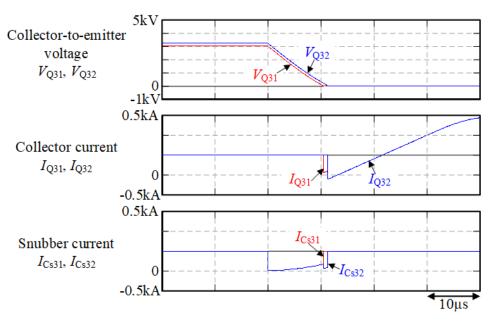

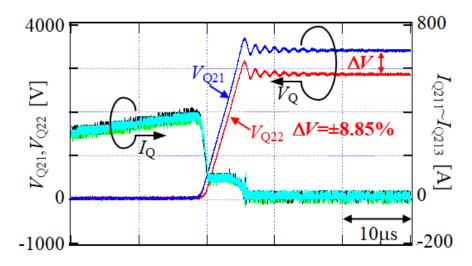

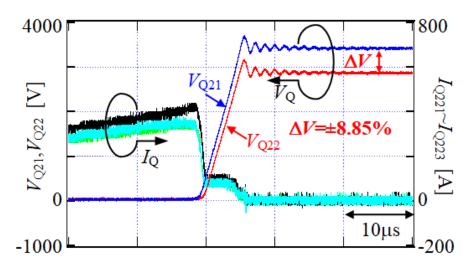

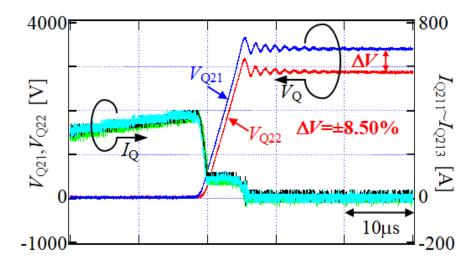

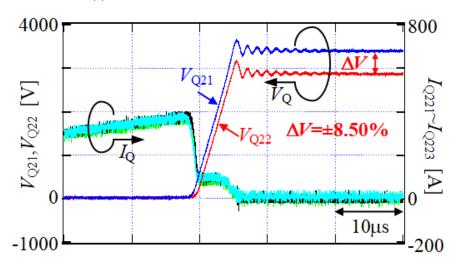

図 4.15 および図 4.16 に表 4.2 に示す組み合わせでの試験波形を示し、表 4.3 に実験波形より測定したオン状態における定常的な電流のアンバランス $\Delta I_{ste}$ ,スイッチング時の過渡的な電流アンバランス $\Delta I_{tra}$ ,電圧アンバランス $\Delta V$  をそれぞれ示す。下側素子のゲート信号を 500ns 遅延させたことにより、上側素子が先にターンオフし、上側素子のスナバキャパシタの充電が先に始まるため、図 4.15 および図 4.16 に示すように上側素子の電圧  $V_{Q21}$  が下側素子の電圧  $V_{Q22}$  が下側素子の電圧  $V_{Q21}$  が下側素子の電圧  $V_{Q22}$  に対して大きくなっていることが確認できる。

図 4.15(a)および表 4.3 に示すようにペア A の上側素子では,  $Q_{212}$ の  $V_{ce(sat)}$ が他の素子( $Q_{211}$ お よび  $Q_{213}$ )に比べて小さく  $Q_{212}$  の電流 IQ212 の電流は  $I_{Q211} \sim I_{Q213}$  の中で最大となるが、 $V_{ce(sat)}$ のバラつきは 0.1V 程度(他の素子に比べて-2.36%)と小さいため,  $\Delta I_{ste}$  は+2.42%とわずかな値 となっている。また、 $V_{\text{ee}(\text{th})}$ の差も同様に小さく並列素子間でほぼ一致しているため、 $\Delta I_{\text{tr}}$ a は +2.19%となっている。一方で,図 4.15(b)および表 4.3 に示すようにペア A の下側素子では,  $Q_{222}$ の  $V_{ce(sat)}$ が他の素子( $Q_{221}$ および  $Q_{223}$ )に比べて 0.3V 程度(他の素子に比べて-6.74%)小さい ため、 $Q_{222}$   $\mathfrak{o}$ 電流  $I_{0222}$  は  $I_{0221} \sim I_{0223}$  の中で最大となり、 $\Delta I_{\mathsf{ste}}$  が+10.3% と上側素子に比べて大き くなる。また, $\Delta I_{

m m}$ も+19.8%とバラつきが大きくなっていることが確認できる。 $\Delta V$ について は、±8.55%であり目標値±10%以下を満足している。ペアBについては、図4.16および表 4.3 に示すように,上側素子および下側素子の  $V_{

m ce(sat)}$ はほぼ等しく, $V_{

m ce(th)}$ も同様にほぼ等しい ため、 $I_{\rm Q211}$ または $I_{

m Q222}$ は並列素子間の電流の中で最大となるが、 $\Delta I_{

m ste}$ および $\Delta I_{

m tra}$ は、それぞれ わずかな値となっており、電流が良くバランスしていることが確認できる。また、ΔV は± 8.50%となっており,目標値±10%以下を満足していることが確認できる。以上の結果は,IGBT の並列接続においては、配線インピーダンスの均一化だけでなく、ペア B やペア A の上側素 子のように,素子特性が近いもの同士が並列になるように組み合わせることが必要になる。 本論文においては、IGBT モジュール購入時に添付される出荷試験データに基づいた組み合わ せによりスイッチング試験を実施した。結果、特性をそろえた組み合わせでは、電流が良く バランスすることを確認した。なお,実際には連続的にスイッチングが行われており,本論 文の試験時よりも高温で各 IGBT が動作することになり、電圧アンバランスの要因である V<sub>ss(th)</sub>が変動することになるが,特性が近い IGBT 同士を組み合わせて 2S3P-IGBT としている 点と、同一の冷却フィン上に実装されることから、各 IGBT の温度は等しく、特性は同様の幅 で変化することが予想される。また、スナバキャパシタには設計マージンを見込んでおり、 特性の変動は設計マージンで吸収されると考えることができる。

(a) 下アーム上側 IGBT のスイッチング波形

(b) 下アーム下側 IGBT のスイッチング波形図 4.15 ペア A でのスイッチング試験結果

(a) 下アーム上側 IGBT のスイッチング波形

(b) 下アーム下側 IGBT のスイッチング波形図 4.16 ペア B でのスイッチング試験結果

表 4.3 スイッチング試験結果

| Item                |             | Pair A<br>(図 4.15) | Pair B<br>(図 4.16) |

|---------------------|-------------|--------------------|--------------------|

| $\Delta I_{ m ste}$ | Top side    | +2.42%             | +1.33%             |

|                     | Bottom side | +10.3%             | +1.30%             |

| $\Delta I_{ m tra}$ | Top side    | +2.19%             | +1.78%             |

|                     | Bottom side | +19.8%             | +0.276%            |

| $\Delta V$          | -           | ±8.85%             | ±8.50%             |

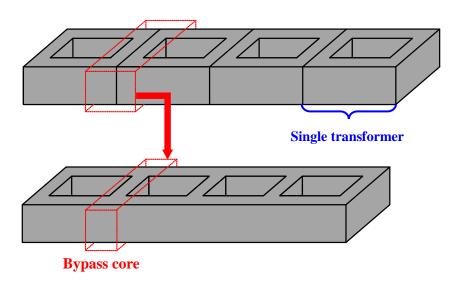

#### 4.5. 変圧器の鉄心構造

前述の通り、半導体素子の2直列接続を実現することで、必要な変圧器数を半減させることが可能となるため、システムの小型高効率化が期待できる。また、第3章で説明したように、多重変圧器では、1つの主鉄心と複数の巻き線で構成することができるため、複数台の変圧器を1台にまとめることが可能となる。したがって、高圧 DC/DC 変換器における変圧器の鉄心構造を多重変圧器と同様にすることで、変圧器鉄心の小型化と変圧器の設置面積削減が期待できる(11)-(14)。