# 電子走査アレーアンテナの高性能化に向けたマイクロ波制御回路技術に関する研究 2024 年 8 月

千葉大学大学院融合理工学府 基幹工学専攻 電気電子工学コース 平井 暁人

# (千葉大学審査学位論文)

電子走査アレーアンテナの高性能化に向けたマイクロ波制御回路技術に関する研究 2024 年 8 月

千葉大学大学院融合理工学府 基幹工学専攻 電気電子工学コース 平井 暁人

# Research on microwave control circuit technology for improving the performance of active electronically steered array antennas

#### Akihito Hirai

#### Abstract

Active Electrical Steered Array (AESA) antennas with microwave modules connected to each element antenna allow for high-speed beam steering by electronic control of the excitation phase. Furthermore, optimizing the excitation amplitude of each element antenna enables low sidelobe. Therefore, AESA is suitable for various applications such as radar, communication, and remote sensing. Wideband, high-precision beam control, low sidelobe, low power consumption, and cost reduction are essential technical challenges for social implementation in various scenes. The key to achieving high performance of AESA is the enhancement of microwave modules because the microwave module determines the beam quality, such as beam direction accuracy and sidelobe. Microwave modules consist of microwave circuits such as phase shifters that control the phase of microwaves, variable gain amplifiers that control the amplitude of microwaves, and phase detectors that detect phase differences between adjacent modules. These microwave control circuits require wideband, high-precision phase control and detection, amplitude control implementation, low power consumption, and cost reduction.

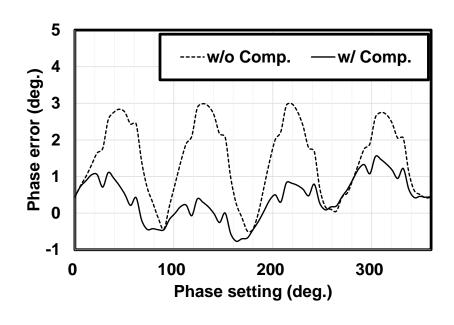

This research aims to enhance the phase and amplitude control related to microwave control circuit technologies, particularly phase shifting, phase detection, and variable gain technologies used in MMIC with silicon semiconductors for high-performance AESA microwave modules. In particular, we focused on microwave control circuits such as a wideband phase shifter, a high-precision phase detector, and a high-precision variable gain phase shifter. For the wideband phase shifter, we proposed a "phase shifter using a g<sub>m</sub>-C polyphase filter" which uses the transistors and capacitors in the IQ generator of vector-sum phase shifters (VSPSs). The proposed VSPS demonstrated a low phase shift error of less than one degree in the C-band. For a high-precision phase detector, we proposed a "phase detector using a fully symmetric mixer and tunable LPF". The proposed phase detector demonstrated a phase detection error of less than two degrees in the C-X band. For a high-precision variable gain phase shifter, we proposed a "variable gain phase shifter with phase compensation using varactors," which is particularly effective in higher frequency bands. The proposed variable gain phase shifter achieved an error of less than 0.75 degrees in the Ka-band.

For future applications, high-precision beam control and low sidelobe of AESA will become increasingly important. Along with that, the importance of phase shifting technology, phase detection technology, variable gain technology, and variable gain phase shifting technology will also be essential for the future. This research is effective for the future development of various AESA applications.

# 内容

| 1章  | 序論                | j                               | 1  |

|-----|-------------------|---------------------------------|----|

| 1.1 | 1. 研              | 究背景                             | 1  |

|     | 1.1.1.            | 電子走査アレーアンテナ(AESA)               | 1  |

|     | 1.1.2.            | AESA におけるマイクロ波制御回路の技術動向         | 5  |

| 1.2 | 2. 従              | 来技術の課題と開発する技術                   | 10 |

| 1.3 | 3. 論              | 文の構成                            | 12 |

| 1.4 | 4. 参              | 考文献                             | 14 |

| 2章  | 位相                | 制御、振幅制御に関わるマイクロ波制御回路の原理         | 18 |

| 2.1 | 1. 移              | 相器                              | 18 |

| 2.2 | 2. 位              | 相検出器                            | 20 |

| 2.3 | 3. 可              | 変利得増幅器                          | 21 |

| 2.4 | 4. 参              | 考文献                             | 23 |

| 3章  | g <sub>m</sub> -( | こポリフェーズフィルタを用いた広帯域な移相器          | 26 |

| 3.1 | 1. ま              | えがき                             | 26 |

| 3.2 | 2. 移              | 相器の回路構成と設計法                     | 27 |

| :   | 3.2.1.            | 従来回路の問題点                        | 27 |

| :   | 3.2.2.            | 提案する回路構成と動作原理・設計法               | 29 |

| 3.3 | 3. 試              | 作結果                             | 40 |

| :   | 3.3.1.            | 試作回路                            | 40 |

| :   | 3.3.2.            | 測定結果                            | 45 |

| 3.4 | 1. t              | すび                              | 55 |

| 3.5 | 5. 参              | 考文献                             | 57 |

| 4章  | 完全                | 対称型ミクサとチューナブル LPF を用いた高精度な位相検出器 | 60 |

| 4.1 | 1. ま              | えがき                             | 60 |

| 4.2 | 2. 位              | 相検出器の回路構成と設計法                   | 61 |

|     | 4.2.1.            | 従来回路の問題点                        | 61 |

|     | 4.2.2.            | 提案する回路構成と動作原理・設計法               | 62 |

| 4.3 | 3. 試              | 作結果                             | 70 |

| 4   | 4.3.1.            | 試作回路                            | 70 |

| 4   | 4.3.2.            | 測定結果                            | 72 |

| 4.4 | 4. む              | すび                              | 78 |

| 4.5 | 5. 参              | 考文献                             | 79 |

| 5 辛 | ,v =              | カタによる位相補償を適田した直結度な可変利得移相哭       | 01 |

|   | 5.1. | まえ | がき                | 83   |

|---|------|----|-------------------|------|

|   | 5.2. | 可変 | 利得移相器の回路構成と設計法    | 84   |

|   | 5.2. | 1. | 従来回路の問題点          | 84   |

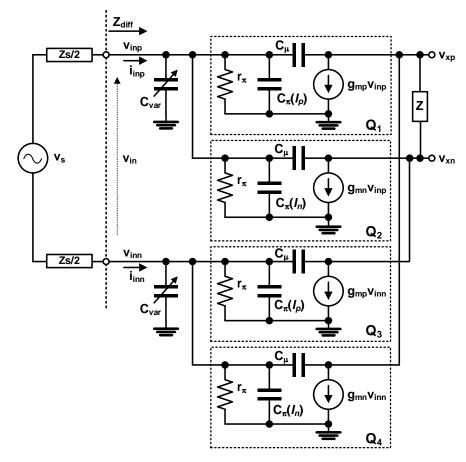

|   | 5.2. | 2. | 提案する回路構成と動作原理・設計法 | 84   |

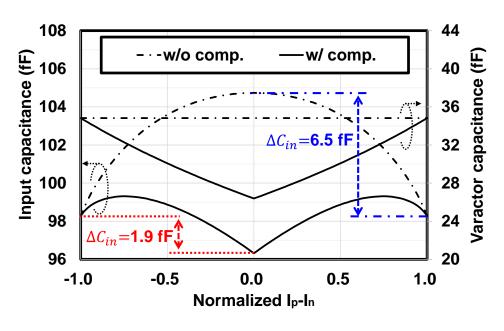

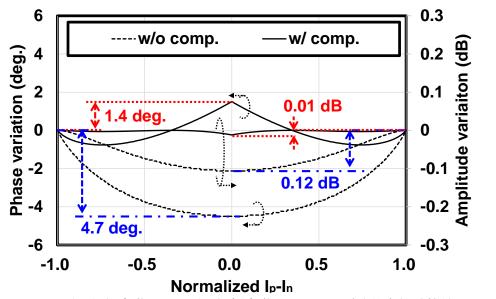

|   | 5.3. | 試作 | :結果               | 95   |

|   | 5.3. | 1. | 試作回路              | 95   |

|   | 5.3. | 2. | 測定結果              | 99   |

|   | 5.4. | むす | ・び                | .109 |

|   | 5.5. | 参考 | 文献                | .110 |

| 6 | 章 結  | 論  |                   | .114 |

|   | 6.1  | 参考 | 文献                | .116 |

| 謝 | 辞    |    |                   | .117 |

| 業 | 績一覧  | Ī  |                   | .118 |

|   |      |    |                   |      |

# 1章 序論

# 1.1. 研究背景

#### 1.1.1. 電子走査アレーアンテナ(AESA)

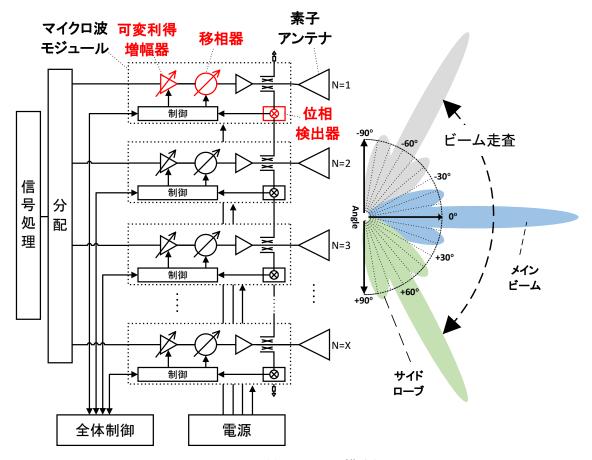

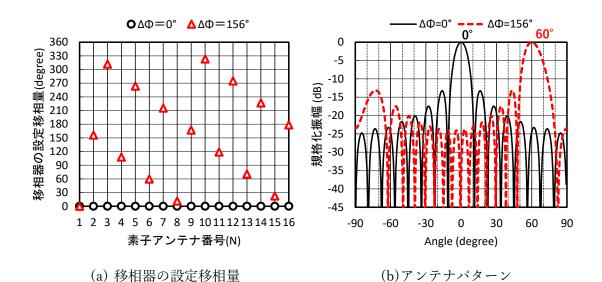

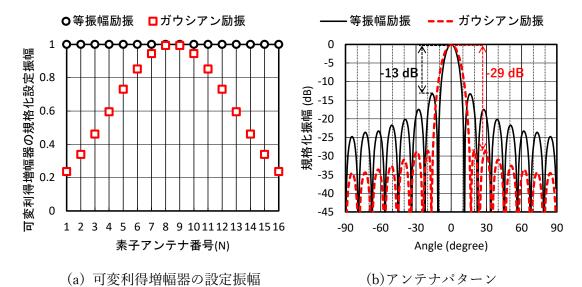

電子走査アレーアンテナ(AESA: Active Electrical Steered Array)は、APAA(Active Phased Array Antenna)とも呼ばれ複数の素子アンテナと、各々の素子アンテナに接続されたマイク ロ波モジュールを備えた高機能なアレーアンテナである[1.1]。図 1-1 に送信 AESA の構成 例を示す。AESA は、マイクロ波モジュールに備えられた移相器(PS: Phase Shifter)により 各素子アンテナの励振位相を電子的に変えることでビーム方向を制御できるため、高速な ビーム操作が可能となる[1.2]。図 1-2 に励振位相制御によるビーム方向制御の例を示す。 図 1-2 は 1 次元 16 素子アンテナ(素子数 N=16)の例で、素子アンテナの間隔は半波長とし ている。図 1-2(a)に示すように隣接するマイクロ波モジュールの出力信号の位相差(ΔΦ) を、移相器により 0°に設定した場合、図 1-2(b)のアンテナパターンに示すように、各アン テナ素子からのビーム複数放射が合成され最もエネルギーが集まるビームの方向、すなわ ち有効放射パターン(メインローブ)の方向  $\theta$  は正面方向 $(0^\circ)$ となる。一方、 $\Delta \Phi$ を  $156^\circ$ とした場合、メインローブは+60°の方向に形成される。このように、AESA は各素子アンテ ナの励振位相を移相器によって電子的に変えることで、機械的な駆動を伴うことなくメイ ンローブの方向 $\theta$ を所望の方向にむけることが可能となる。さらにマイクロ波モジュール に可変利得増幅器(VGA: Variable Gain Amplifier)を備えることにより、各素子アンテナの 励振振幅を精度よく制御することができ、励振振幅分布を最適化することで所望方向以外 にエネルギーが集まる現象であるサイドローブを抑制することが可能となる[1.3]。図 1-3 に励振振幅制御によるサイドローブ抑制の例を示す。図 1-2 と同様のアンテナ構成で 16 素 子をすべて等振幅で励振としたときと、ガウシアン分布で励振したときのアンテナパター ンの計算結果である。16 素子全て等振幅で励振した場合、メインローブの隣に形成される サイドローブが-13 dB となるのに対し、ガウシアン分布で励振した場合には、サイドロー ブを-29 dB まで抑制することができ所望方向以外への干渉の低減が可能となる。

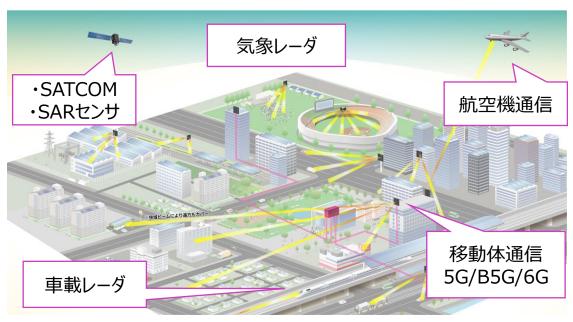

上記に示す特徴により AESA は図 1-4 に示すような様々なアプリケーションに応用されている[1.4]。AESA はレーダ用アンテナとして、国内では 1970 年~1980 年代に X 帯(8~12 GHz)で実用化された[1.5]。AESA は、機械駆動型のアンテナに比べビーム走査速度を大幅に向上できるため移動・固定レーダにおいて主流となっており[1.6]、気象レーダでは天候把握におけるリアルタイム性向上の恩恵をもたらしている。近年では、車載レーダに代表されるミリ波帯(30 GHz~) 以上でのアプリケーションに適用されており、距離分解能の観点から、より広い周波数帯域幅への要求が生じている[1.7]。通信分野においては、AESA は特に衛星通信(SATCOM: Satellite Communications)や航空機通信、地上移動体通信といった移動体通信分野に応用されている。2008 年に Ka 帯(26~40 GHz)超高速インターネット

通信衛星が打ち上げられ、日本列島全域を含む広範囲な地域で通信回線を確保できるようなった [1.8]。近年では周波数資源の枯渇に伴い  $Q(33\sim50~{\rm GHz})/{\rm V}(40\sim75~{\rm GHz})/{\rm E}(71-76/81-86~{\rm GHz})/{\rm W}(75-110~{\rm GHz})$ 帯といったより高い周波数帯での動作、またさらなる高速通信実現のためのより広い周波数帯域幅の確保にむけた開発が加速している [1.9]。地上移動体通信においても AESA の実用化が進んでおり、第 5 世代移動通信システム(5 G)における適用 [1.10]、さらには、その後継となり 2030 年代に導入が想定されている次世代の情報通信インフラである B5G/6G での候補となっているサブテラヘルツ帯においても必須の技術として開発が加速している [1.11]。リモートセンシング分野においては、2006 年に打ち上げられた 陸域観測技術衛星だいち (開発名 ALOS: Advanced Land Observing Satellite) [1.12]や、また、その後継として 2014 年に打ち上げられただいち 2 号機(開発名: ALOS2)には、L 帯  $(0.5\sim2~{\rm GHz})$ の AESA により高分解能を可能とした SAR(Synthetic Aperture Radar)センサが搭載され、地図作成、地域観測、災害状況把握などに貢献している [1.13]。

以上のように、AESA はレーダ、通信、リモートセンシングといった様々なアプリケーションで応用されており、広帯域化やビーム制御高精度化、低サイドローブ化、低消費電力化、低コスト化といった高性能化は、AESA の広いシーンにおける社会実装のための重要な技術課題である。

図 1-1 送信 AESA の構成例

図 1-2 励振位相制御によるビーム方向制御の例

図 1-3 励振振幅制御によるサイドローブ抑制の例

図 1-4 AESA のアプリケーション例[1.4]

#### 1.1.2. AESA におけるマイクロ波制御回路の技術動向

AESA を構成するコンポーネントにおいて、特に重要なものに図 1-1 内に示すマイクロ波モジュールがある。マイクロ波モジュールには、制御部からの制御信号を用いてマイクロ波の位相を制御する移相器、振幅を制御する可変利得増幅器、隣接するモジュール毎の位相差を検出する位相検出器などのマイクロ波制御回路から構成される。マイクロ波制御回路がAESAのビーム制御の基本機能を司り、ビーム方向の正確性、サイドローブ量といったビーム品質を決定するため、AESAの広帯域化やビーム制御高精度化、低サイドローブ化、低消費電力化、低コスト化といった高性能化のためには、マイクロ波制御回路の広帯域化、位相制御・位相検出の高精度化、振幅制御の実装、低消費電力化、低コスト化といった高性能化が必要となる。低コスト化においては、半導体に実装されるマイクロ波制御回路のコストはチップサイズに依存するため、回路サイズの小型化が重要となる。

マイクロ波制御回路は、その時々に実現可能なデバイスの特徴に応じた開発がなされてきた[1.14]。初期のマイクロ波制御回路は、低損失で、高い電力特性を有する受動デバイスであるフェライトデバイスを用いたものが主流であり、1950年代~1960年代に盛んに研究された[1.15][1.16]。その後、高性能化のために増幅器を搭載した能動回路によるマイクロ波モジュールの開発が進み、同時に小型、軽量、低消費電力化が要求されるようになった。

フェライトデバイスでは不可能であった小型、軽量、低消費電力を実現するため、1970年代以降から半導体デバイスを装荷したマイクロ波集積回路(MIC: Microwave Integrated Circuit)が盛んに開発されるようになった[1.17][1.18]。初期の半導体デバイスとしては、構造が比較的簡単で高周波特性の優れた PIN ダイオードなどのダイオードが用いられた。これにより、マイクロ波回路単体で数 cm~10 cm 角への小型化が可能になったものの、ダイオードは電流駆動型デバイスであったため多数のマイクロ波モジュールを用いる AESA では消費電力が大きくなるという問題があった。

1980 年代以降、電圧駆動で電力を消費しない半導体デバイスである電界効果トランジスタ (FET: Field Effect Transistor) [1.19]の利用が主流となった。さらにガリウム砒素(GaAs)などの化合物半導体基板上に、容量やインダクタといったトランジスタ以外の受動デバイスも集積した MMIC (Monolithic Microwave Integrated Circuit) が登場する。これにより、一つのマイクロ波モジュールは 10 cm 角程度に小型化できるようになり、また、それに伴う軽量化、低消費電力化が進むとともに、その優れた量産均一性はアレーアンテナを均一動作させる上での画期的な進歩を起こした[1.20][1.21]。

1990 年代になると FET より電子移動度が高い HEMT(High Electron Mobility Transistor)[1.22]が実用化され、マイクロ波制御回路の高周波化が進むとともに、必要となるマイクロ波制御回路を MMIC 内に搭載することによる高度なチップ集積化による小型化が進み、数 cm 角のマイクロ波モジュールが登場する[1.23]。一方、マイクロ波制御回路の制御に必要となる電力管理、移相量や振幅の設定、AESA として動作するための校正データの記憶などに必要となるディジタル制御回路は化合物半導体基板上では実現できず、マイ

クロ波モジュール内に別チップが必要となる。そのため、化合物半導体では1チップでマイクロ波モジュールを実現することによる数 cm 角以下への小型化は困難であった[1.24]。

2000 年代になると、シリコン半導体(Si)がマイクロ波帯の周波数で動作可能となり、 MOSFET(Metal Oxide Semiconductor Field Effect Transistor) № HBT(Heterojunction Bipolar Transistor)といったシリコントランジスタが登場し、P 型と N 型の MOSFET を使 用可能な CMOS(Complementary Metal-Oxide-Semiconductor)や、CMOS より高速な HBT、 HBT と、HBT より低消費電力な CMOS を同時に使用可能な BiCMOS(Bipolar CMOS)を 用いたマイクロ波制御回路の開発が活発化していった[1.25]。 化合物半導体と比較しシリコ ン半導体には、マイクロ波制御回路のみならず、その制御に必要なディジタル制御回路を同 じチップ内に搭載できる。その集積度の高さ、微細化による高周波数への拡張性、大ウェハ 径による低コスト化と優れた量産性から、数 GHz 以上のマイクロ波やミリ波帯をターゲッ トに盛んに開発が行われた[1.26]。2010 年代以降、シリコン半導体の微細化に伴うさらな る高周波化、小型化が進み、4 素子~16 素子分のアンテナに対応する複数のマイクロ波モ ジュールを 1cm 角以下の 1 チップに搭載したビームフォーミング IC と呼ばれる高集積化 技術が盛んに開発された[1.27]。これらのマイクロ波モジュールの高集積化技術の進化に加 え、樹脂基板への半導体チップの実装技術の進化により、樹脂基板の表面にアンテナを形成 し、裏面にシリコン1チップによるマイクロ波モジュールを表面実装するのみという、非常 にシンプルな構造をしたフラットパネル型 AESA が誕生しさらなる低コスト化が進んだ。 これらの恩恵により、5G、航空機搭載衛星通信といったより低コスト化が求められるアプ リケーションへの適用に繋がっている[1.28] [1.29]。

このように、マイクロ波モジュール、マイクロ波制御回路の歴史はデバイスの発展とともにあるが、一方でデバイスに適したマイクロ波制御回路の回路構成、および設計法も同時に発展してきた。

表 1-1 にマイクロ波モジュール、マイクロ波制御回路の開発の歴史を示す。フェライトデバイスを用いた初期の分布定数型移相器では、必要となる耐電力特性と所望の移相量特性を同時に得るための伝送線路の回路構成、設計法が研究された[1.14]。MIC においては、初期の半導体デバイスである PIN ダイオードを用いた移相器において、低通過損で所望の移相量特性を得るための回路構成、設計法が研究された[1.30]。PIN ダイオードによる可変減衰器では、PIN ダイオードの実装に伴う寄生成分を考慮しつつ広帯域特性を得るためのMIC 可変減衰器の回路構成、設計法などが研究された[1.17]。化合物半導体を用いた MMIC へと移行してくると、FET を用いた単純で広帯域なバイアス回路を構成するとともに、1つの回路に多数の FET と、集中定数の受動素子を配列する回路構成、設計法が登場し、その一例として MIC 移相器では実現が難しかった直流~50 GHz という非常に広帯域なMMIC 可変利得減衰器が報告された[1.31]。FET を用いた移相器では従来の分布定数型の受動素子を集中定数型におきかえることで、個別の回路サイズとしては数 mm~1 cm 角程度で、数°-rms の移相量誤差を実現する MMIC 移相器が実現された[1.32]。

シリコン半導体が登場すると、MMIC 内で用いることができるデバイスの自由度が飛躍的に向上し、化合物半導体において主要な方式であった受動素子だけでなく、能動素子を用いた回路構成、設計法が登場する。これにより、個別の回路サイズとしては数 100 µm 角以下、数 10mW 以下での能動素子による MMIC 移相器の登場し、また、これまでの主要な回路構成である可変減衰器から通過利得を有する能動素子による MMIC 可変利得増幅器への回路構成の移行が進み、マイクロ波制御回路の小型化、低消費電力化といった高性能化が加速していく。さらには、これまで使用できるデバイスの制限から困難であった複数のマイクロ波モジュールの位相差を検出する小型な位相検出技術が登場し、AESA の高機能化もさらに加速していくこととなる。

移相器では、ベクトル合成型移相器(VSPS: Vector Sum Phase Shifter)[1.33]という回路 構成が新たに実用化され、1.5º-rms 程度の低移相量誤差を実現する設計法[1.34]や、X 帯~ Ka 帯まで対応可能な広帯域な回路構成、設計法[1.35]が開発された。可変利得増幅器では、 電流の量を変更するカレントステアリング方式[1.36]や負荷をディジタル信号によって変 更する方式[1.37]といった回路構成、設計法が登場し、制御設定値に対し出力が 10・LOG(制 御設定値)で変化できるものや、78 dB 以上の非常に広い振幅制御範囲を有するもの、設定 値に対しての振幅設定誤差が低い制御技術[1.38]など、高性能化を実現する回路構成、設計 法が開発された。近年では移相器と可変利得増幅器を一つの回路で構成する可変利得移相 器(VGPS: Variable Gain Phase Shifter)という回路構成も提案され、さらに小型で低消費電 力な回路構成、設計法が提案されている[1.39]。また、複数のマイクロ波モジュールを1チ ップに搭載したビームフォーミング IC においては、移相器や可変利得増幅器を一つのチッ プ内に複数実装し、それらに高周波数信号を分配・合成する回路や制御・電源回路も含め実 装する回路構成が開発され、チップサイズ数 mm<sup>2</sup>の中に 4~16 素子分のマイクロ波モジュ ールを搭載し、送信 1 素子あたりで 100~200 mW、受信 1 素子当たりで 50~100 mW と いう非常に低い消費電力でマイクロ波モジュールを実現している[1.39]。 位相検出技術つい ては、近年の AESA の大規模化に伴う新たな課題に対する解決案として開発されている。 AESA の大規模化に伴い、アンテナ開口の温度差分布やマイクロ波モジュールの製造ばらつ きに起因するマイクロ波モジュール毎の設定移相量ばらつきが無視できなくなり、ビーム 方向やヌル点方向の角度誤差が生じビーム品質が劣化するという問題が生じている。この 問題に対し、マイクロ波モジュール内やビームフォーミング IC 内に小型な位相検出器を設 け素子アンテナの励振位相の誤差を検出し、移相量制御値に反映させることで AESA の励 振位相の高精度化を実現する技術が報告されている[1.41]。本機能は、Built-In Self-Test 機 能として近年注目されている技術であり、大規模 AESA や 1~2°以下の低い移相量誤差が求 められる AESA を実現する際に必要な技術となっている[1.42]。

このように、マイクロ波制御回路に適した回路構成、設計法は新しいデバイスが実用化されるたびに研究されてきており、回路構成、設計法の研究はマイクロ波制御回路の発展に不可欠であり、今後も重要である。高性能なデバイス実用化に加え、そのデバイスを使いこな

す回路構成、設計法が、マイクロ波モジュールの高性能化をもたらし、更には AESA の高性能化を可能にすると考えられる。

表 1-1 マイクロ波モジュール、マイクロ波制御回路の開発の歴史

|            | $\sim$ 1960                                                | 1970                                                                                                                                                                                                                | 1980               | 1990                                                             | 2000 | 2010                                                    | 2020      |

|------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------|------|---------------------------------------------------------|-----------|

|            | ・フェライト                                                     | 8                                                                                                                                                                                                                   |                    |                                                                  |      |                                                         |           |

|            |                                                            | ・Si-PINダイオード                                                                                                                                                                                                        |                    |                                                                  |      |                                                         |           |

|            |                                                            | ・ショットキーバリアダイオード                                                                                                                                                                                                     | · GaAs—MESFET      |                                                                  |      |                                                         |           |

| ゴバノン井代     |                                                            | ・バラクタダイオード                                                                                                                                                                                                          |                    | · GaAs—HEMT                                                      |      |                                                         |           |

| アハイ ヘ松門    |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | · Si-CMOS                                               |           |

|            |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | · Si-BiCMOS                                             |           |

|            | <ul><li>分布定数型移相器</li></ul>                                 |                                                                                                                                                                                                                     |                    |                                                                  |      |                                                         |           |

|            | ・数10 cm角/マイクロ波回路                                           | ·MIC移相器                                                                                                                                                                                                             |                    |                                                                  |      |                                                         |           |

|            |                                                            | ·MIC可変減衰器                                                                                                                                                                                                           | ・集中定数を含む受動         | 集中定数を含む受動素子によるMMIC移相器                                            |      |                                                         |           |

|            |                                                            | ・数 cm角/マイクロ波回路                                                                                                                                                                                                      | ・集中定数を含む受動         | ・集中定数を含む受動素子によるMMIC可変減衰器                                         |      | ・能動素子によるMMIC移相器                                         | 器         |

|            |                                                            |                                                                                                                                                                                                                     | ・数 cm角/マイクロ波モジュール  | モジュール                                                            |      | ・能動素子によるMMIC可変利得増幅器                                     | 5利得增幅器    |

|            |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | ・小型な位相検出技術                                              |           |

|            |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | ・ $\sim 1  \mathrm{cm}$ 角/ $\sim 16$ 素子のビームフォーマIC       | -ムフォーマIC  |

|            |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | · ≒100 mW/1素子                                           |           |

| 回路構成.      | 03                                                         |                                                                                                                                                                                                                     | Digital Controller | preampilier Driver Ampiliter power Ampiliter                     | iei  | Blas Array Decoder                                      |           |

| 力士司        |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | CH-#C                                                   | = C CH-5- |

| Z. I I Z   |                                                            |                                                                                                                                                                                                                     |                    |                                                                  |      | CH3                                                     | CH-6      |

|            |                                                            |                                                                                                                                                                                                                     |                    |                                                                  | _    | A A S A S A S A S A S A S A S A S A S A                 | OH2       |

|            | 3                                                          |                                                                                                                                                                                                                     |                    |                                                                  |      | CNAB Phase Shifter                                      |           |

|            |                                                            | Fig. 11. Theotograph of L-band switched line 4-bit aumma microstrip place and switching of this development were supported by the Navul Research Laboratories, Washington, D. C., under Contract N00014-72-C-6213.) |                    |                                                                  |      | Single Channel Address: 000                             | CH-8-     |

|            | Fig. 12 Photograph of rotary-field phase shifters          |                                                                                                                                                                                                                     | Attenuate Pha.     | Phase Sh. Postamplin LNA Switch Hus.                             |      | 190 1 100000 100                                        | ••••      |

|            | マイクロ波回路                                                    | マイクロ波回路                                                                                                                                                                                                             | JONE .             | 49IIId                                                           | Puo  | ビームフォーマーIC                                              | <u></u>   |

|            | (移相器)単体写真                                                  | (移相器)単体写真                                                                                                                                                                                                           | 717                | マイクロ波モジュール(1素子分)写真                                               |      | (マイクロ波モジュール8素子分)写真                                      | 8素子分)写真   |

|            | $(6 \text{ cm} \times 17 \text{ cm} \times 20 \text{ cm})$ | $(3 \text{ cm} \times 5 \text{ cm} \times 1 \text{ cm})$                                                                                                                                                            | (1.)               | $(1.6 \text{ cm} \times 4.6 \text{ cm} \times 0.5 \text{ cm})^*$ |      | $(2.5~\text{mm}\times2.5~\text{mm}\times1.0~\text{mm})$ | < 1.0 mm) |

|            | [1.13]                                                     | [1.16]                                                                                                                                                                                                              |                    | [1.22]                                                           |      | [1.23]                                                  |           |

| ※写直からの見待もり | (精制)                                                       |                                                                                                                                                                                                                     | •                  |                                                                  |      |                                                         |           |

## 1.2. 従来技術の課題と開発する技術

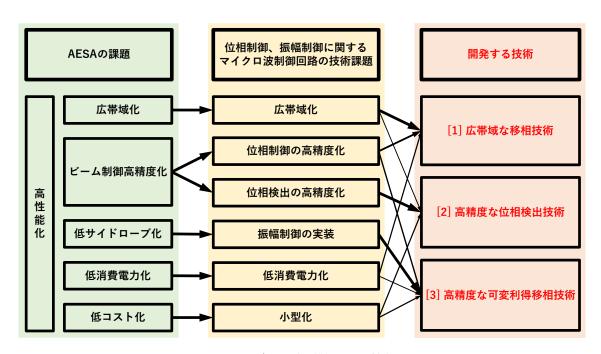

前節で述べた技術動向を踏まえ、高性能な AESA 用マイクロ波モジュールを実現するために、AESA のビーム品質を左右するマイクロ波の位相制御、振幅制御に関わるマイクロ波制御回路技術のうち、特にシリコン半導体での MMIC で用いられる移相技術、位相検出技術、可変利得技術に対する研究開発を目的とする。図 1-5 に各課題と開発する技術について示す。ここでは、以下の3つを研究対象とし開発する技術として位置付ける。

開発する技術[1] : 広帯域な移相技術

開発する技術[2] : 高精度な位相検出技術

開発する技術[3] :高精度な可変利得移相技術

#### 開発する技術[1] : 広帯域な移相技術

マイクロ波の位相を制御する移相器は、正確なビーム制御機能を実現するための重要な 回路の一つである。ここでは、AESA の広帯域化をメインターゲットとし、広帯域に低移相 量誤差を実現する移相技術の開発を実施する。シリコンデバイスで主要な移相器の方式で あるベクトル合成型において、直交信号を生成する I/Q 生成器が必要となる。I/Q 生成器 は受動回路のため、一定の移相量誤差を実現する周波数帯域と通過損失量はトレードオフ の関係となり、ある周波数範囲で低移相量誤差を実現する場合に通過損失が増大する。その 通過損失を補償する増幅回路が必要となるため消費電力が増加し、結果、帯域内移相量誤差 と消費電力がトレードオフの関係となる。そこで、このトレードオフを解消し、広帯域に低 移相量誤差性能を実現する移相器の回路構成、設計法を開発する。

#### 開発する技術[2] : 高精度な位相検出技術

AESA のビーム制御高精度化をメインターゲットとし、隣接するモジュール間の位相を高精度に検出する位相検出技術の開発を実施する。前節で示したように多数の素子アンテナからなる大規模アレーアンテナでは、各マイクロ波モジュール出力における励振位相が、モジュールの温度や製造ばらつきによって変動し、ビーム特性が変化するという問題がある。高精度な励振位相分布を実現するためには、励振位相を高精度に管理する必要がある。励振位相を高精度に管理するための一つの手段として、隣接モジュール間の高精度な位相検出器がある。そこで、隣接モジュール間の位相を高精度に検出する位相検出器の回路構成、設計法を開発する。

#### 開発する技術[3] : 高精度な可変利得移相技術

AESA の低サイドローブ化のため、マイクロ波の振幅制御を小型に実装する技術開発を実施する。AESA を構成する素子アンテナ間の距離は半波長が基本となるため、特にミリ波以

上の高周波帯において小型な実装技術が必要となる。例えば30 GHz では半波長は5 mm となり、25 mm²以下という限られた面積に移相機能と可変利得機能の2つを実装する必要がある。移相機能と可変利得機能を同一回路で実装する可変利得移相器によって小型化が可能だが、利得制御に伴って通過位相が変化し移相量誤差の劣化要因となる。そこで、高精度な可変利得移相器の回路構成、設計法を開発する。

図 1-5 各課題と開発する技術

#### 1.3. 論文の構成

本研究の目的は、上記で述べたマイクロ波制御回路技術の技術課題を解決することである。図 1-6 に本論文の構成を示す。第 1 章では序論、第 2 章では位相制御、振幅制御に関わるマイクロ波制御回路の原理について示す。第 3 章~第 5 章は、1.2 節で示した高性能な AESA 用マイクロ波モジュールを実現するために必要となる、「開発する技術[1]~[3]」に ついて実施した研究結果について示す。具体的には、第 3 章では「開発する技術[1]:広帯域な移相技術」、第 4 章では「開発する技術[2]:高精度な位相検出技術」、第 5 章では「開発する技術[3]:高精度な可変利得移相技術」に関する研究についてそれぞれ示し、第 6 章で結論を示す。以下に、各章の概要を述べる。

第 1 章は序論であり、マイクロ波の位相制御、振幅制御に関わるマイクロ波制御回路の研究背景と、従来技術の課題、開発する技術について示す。

第2章はマイクロ波の位相制御、振幅制御に関わるマイクロ波制御回路である、移相器、 位相検出器、さらに、可変利得移相器のベースとなる可変利得増幅器の動作原理について述 べる。

第 3 章は広帯域な移相技術について述べる。広帯域な移相技術として、ベクトル合成型の移相器において一般的に用いられる抵抗と容量で構成される I/Q 生成器の抵抗をトランジスタに置き換えた「gm-C ポリフェーズフィルタを用いた広帯域な移相器」を提案する。本回路の周波数特性および最大利得、移相量誤差、調整可能な周波数範囲を理論的に示し、広帯域に低移相量誤差を実現する方法を示す。提案する移相器を S 帯で試作した結果について述べ、提案する回路構成と設計法の有効性を示す。

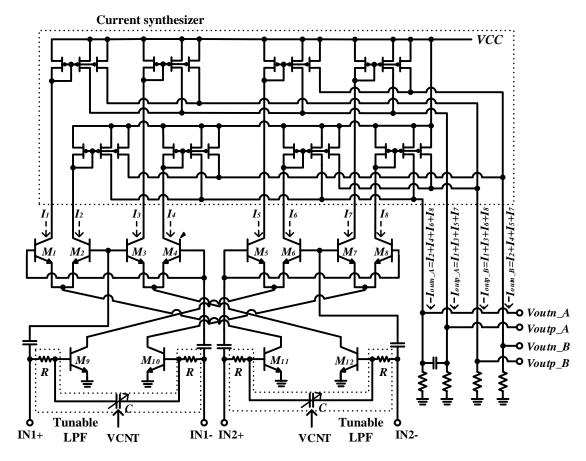

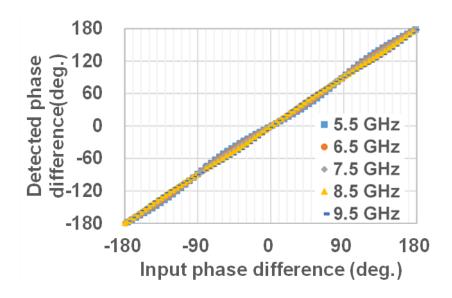

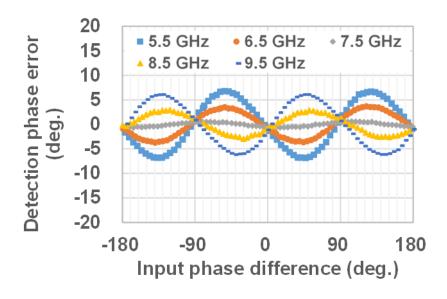

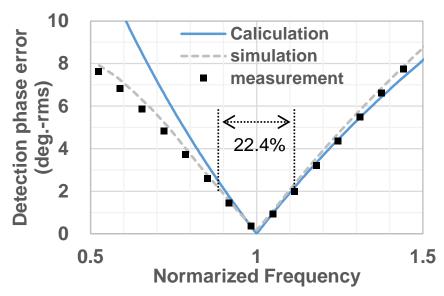

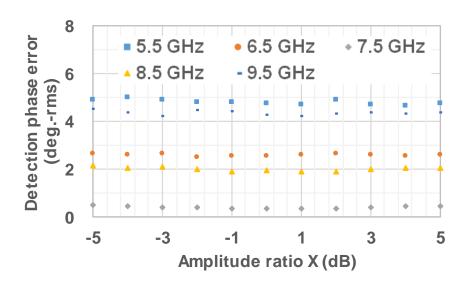

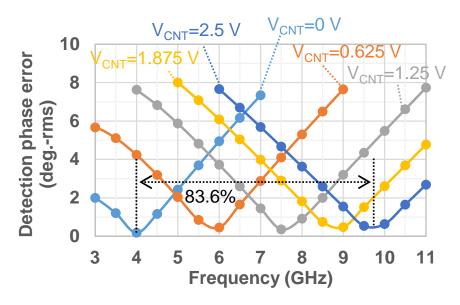

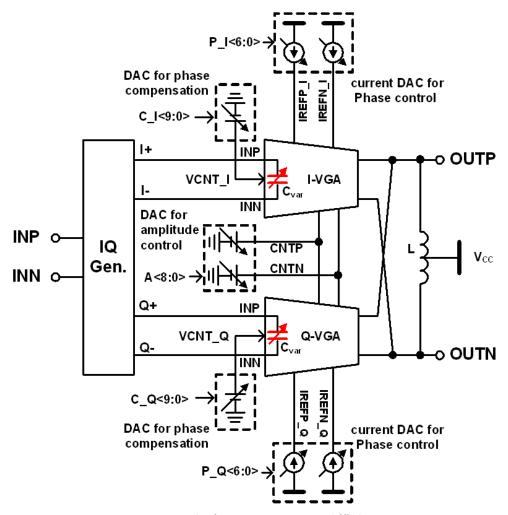

第4章では、高精度な位相検出技術について述べる。高精度な位相検出技術として、「完全対称型ミクサとチューナブル LPF(Low Pass Filter)を用いた高精度な位相検出器」を提案する。完全対称型ミクサと 45°移相器による位相検出器の検出特性が入力振幅に依存しないことに着目し、45°移相器にチューナブルな LPF を適用することで、高精度な位相検出が実現可能となる位相検出器の回路構成と設計法を提案する。提案する位相検出器を C-X 帯で試作した結果について述べ、本回路構成と設計法の有効性を示す。

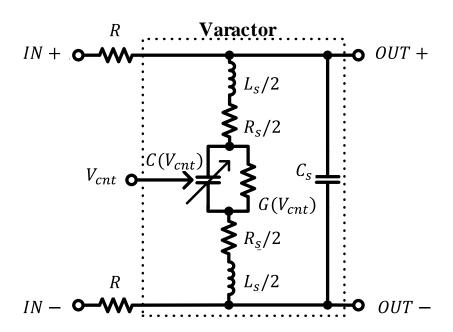

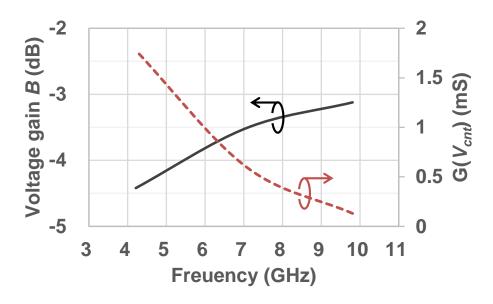

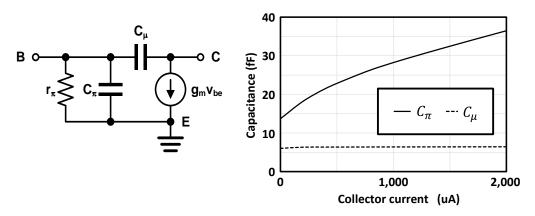

第 5 章では、特に小型な実装が必要となる、より高い周波数帯において有効となる高精度な可変利得移相技術として、「バラクタによる位相補償を適用した高精度な可変利得移相器」を提案する。制御時の入力容量変化によって可変利得移相器の通過位相特性が変化することに着目し、入力段にチューナブルデバイスであるバラクタを搭載した、高精度な可変利得移相器の回路構成と設計法を提案する。提案する設計法に基づき Ka 帯で試作した結果について述べ、本回路構成と設計法の有効性を示す。

第6章は結論であり、本研究で得られた成果を要約する。

# 第1章 序章

#### 第2章 原理

- ・位相制御、振幅制御に関わるマイクロ波制御回路の研究背景

- ・従来技術の課題、開発する技術

- ・マイクロ波制御回路の動作原理

#### 第3章 研究成果1

開発する技術[1]:広帯域な移相技術 「g<sub>m</sub>-Cポリフェーズフィルタを用いた広帯域な移相器」

# 第4章 研究成果2

開発する技術[2]:高精度な位相検出技術 「完全対称型ミクサとチューナブルLPFを用いた高精度な位相検出器」

# 第5章 研究成果3

開発する技術[3]:高精度な可変利得移相技術 「バラクタによる位相補償を適用した高精度な可変利得移相器」

#### 第6章 結論

図 1-6 論文の構成

## 1.4. 参考文献

- [1.1] 高橋 徹, "電子情報通信学会『知識の森』(http://www.ieice-hbkb.org/) 4 群 2 編 7 章 アレーアンテナ"

- [1.2] A. A. Oliner and G.H Knittel, Phased Array Antennas, Artech House Inc., Apr. 1972

- [1.3] N. Herscovici, "Low-sidelobe arrays fed by a uniform-distribution feeding network," in IEEE Antennas and Propagation Magazine, vol. 39, no. 3, pp. 72-74, June 1997, doi: 10.1109/74.598563.

- [1.4] 三菱電機株式会社 通信システム事業部 NTT 営業部 2015 年 3 月 2 日 ニュース リリース NTT ドコモとの 5G 実験協力に合意、概要を「MWC2015」で紹介, http://www.mitsubishielectric.co.jp/news/2015/0302-b.html

- [1.5] I. Chiba, Y. Konishi and T. Nishino, "Progress of phased array systems in Japan," 2010 IEEE International Symposium on Phased Array Systems and Technology, Waltham, MA, USA, 2010, pp. 19-28, doi: 10.1109/ARRAY.2010.5613395.

- [1.6] E. Rai, S. Nishimoto, T. Katada and H. Watanabe, "Historical overview of phased array antennas for defense application in Japan," Proceedings of International Symposium on Phased Array Systems and Technology, Boston, MA, USA, 1996, pp. 217-221, doi: 10.1109/PAST.1996.566088.

- [1.7] M. Maggi et al., "Millimeter-Wave Phased Arrays and Over-the-Air Characterization for 5G and Beyond: Overview on 5G mm-Wave Phased Arrays and OTA Characterization," in IEEE Microwave Magazine, vol. 23, no. 5, pp. 67-83, May 2022, doi: 10.1109/MMM.2022.3148328.

- [1.8] 北尾, 針生, 白松, "超高速インターネット衛星 WINDS 搭載 K 帯アクティブフェーズドアレーアンテナ(APAA),"三菱電機技報, Vol.79, No.8, pp.31-34, 2005

- [1.9] P. Harati et al., "Is E-Band Satellite Communication Viable?: Advances in Modern Solid-State Technology Open Up the Next Frequency Band for SatCom," in IEEE Microwave Magazine, vol. 18, no. 7, pp. 64-76, Nov.-Dec. 2017, doi: 10.1109/MMM.2017.2738898.

- [1.10] W. Hong et al., "mmWave 5G NR Cellular Handset Prototype Featuring Optically Invisible Beamforming Antenna-on-Display," in IEEE Communications Magazine, vol. 58, no. 8, pp. 54-60, August 2020, doi: 10.1109/MCOM.001.2000115.

- [1.11] C. Han, L. Yan and J. Yuan, "Hybrid Beamforming for Terahertz Wireless Communications: Challenges, Architectures, and Open Problems," in IEEE Wireless Communications, vol. 28, no. 4, pp. 198-204, August 2021, doi: 10.1109/MWC.001.2000458.

- [1.12] 村上, 川西, 伊藤, 島田, "フェーズドアレイ方式 L バンド合成開口レーダ PALSAR," 信学技報 SANE2006-66, pp. 11-14, 2006

- [1.13] 大内, "リモートセンシングのための合成開口レーダの基礎,"東京電機大学出版局, 2004

- [1.14] 半谷, "アクティブフェーズドアレーアンテナ用マイクロ波制御回路に関する研究," 東北大学大学院 工学研究科 博士論文, 2012

- [1.15] S. K. Koul, B. Bhat, Microwave and Millimeter Wave Phase Shifters: Dielectric and Ferrite Phase Shifters, Artech House Inc., 1991

- [1.16] C. L. Hogan, "The ferromagnetic Faraday effect at microwave frequencies and its applications: The microwave gyrator," in The Bell System Technical Journal, vol. 31, no. 1, pp. 1-31, Jan. 1952, doi: 10.1002/j.1538-7305.1952.tb01374.x.

- [1.17] H. C. Okean and R. Pflieger, "Octave Ban D MIC Electronically Variable Attenuators Using PIN Diodes," 1971 IEEE GMTT International Microwave Symposium Digest, Washington, DC, USA, 1971, pp. 180-181, doi: 10.1109/GMTT.1971.1122956.

- [1.18] J. F. White, "Diode Phase Shifters for Array Antennas," in IEEE Transactions on Microwave Theory and Techniques, vol. 22, no. 6, pp. 658-674, Jun. 1974, doi: 10.1109/TMTT.1974.1128309.

- [1.19] 葛原, "基礎講座 02 トランジスタ入門" MWE 2010 基礎講座, Dec, 2010

- [1.20] H. Howe, "Microwave Integrated Circuits An Historical Perspective," in IEEE Transactions on Microwave Theory and Techniques, vol. 32, no. 9, pp. 991-996, September 1984, doi: 10.1109/TMTT.1984.1132812.

- [1.21] K. Wilson, "GaAs monolithic microwave integrated circuits," in Electronics and Power, vol. 33, no. 4, pp. 249-251, April 1987, doi: 10.1049/ep.1987.0164.

- [1.22] T. Mimura, S. Hitamizu, T. Fuji and K. Nanbu, "A New Field-Effect Transistor with Selectivity Doped GaAs/n-AlxGal-x As Heterojunctions," Jpn, J. Appliphis., vol. 19, pp. 225-227, May 1980

- [1.23] F. E. van Vliet and A. de Boer, "Fully-integrated core chip for X-band phased array T/R modules," 2004 IEEE MTT-S International Microwave Symposium Digest (IEEE Cat. No.04CH37535), Fort Worth, TX, USA, 2004, pp. 1753-1756 Vol.3, doi: 10.1109/MWSYM.2004.1338936.

- [1.24] B. A. Kopp, M. Borkowski and G. Jerinic, "Transmit/receive modules," in IEEE Transactions on Microwave Theory and Techniques, vol. 50, no. 3, pp. 827-834, March 2002, doi: 10.1109/22.989966.

- [1.25] G. M. Rebeiz and K. -j. Koh, "Silicon RFICs for phased arrays," in IEEE Microwave Magazine, vol. 10, no. 3, pp. 96-103, May 2009, doi: 10.1109/MMM.2009.932078.

- [1.26] D. J. Carlson, C. Weigand and T. Boles, "MMIC based phased array radar T/R modules," The 7th European Radar Conference, Paris, France, 2010, pp. 455-458.

- [1.27] B. Sadhu, X. Gu and A. Valdes-Garcia, "The More (Antennas), the Merrier: A Survey of Silicon-Based mm-Wave Phased Arrays Using Multi-IC Scaling," in IEEE Microwave Magazine, vol. 20, no. 12, pp. 32-50, Dec. 2019, doi: 10.1109/MMM.2019.2941632.

- [1.28] J. -C. S. Chieh et al., "Development of Flat Panel Active Phased Array Antennas Using 5G Silicon RFICs at Ku and Ka-Bands," in IEEE Access, vol. 8, pp. 192669-192681, 2020, doi: 10.1109/ACCESS.2020.3032841.

- [1.29] S. Das et al., "A Flat-Panel 8 × 8 Wideband K-/Ka-Band Dual Circularly Polarized Phased Array Antenna for CubeSat Communications," in IEEE Transactions on Antennas and Propagation, vol. 71, no. 5, pp. 4153-4166, May 2023, doi: 10.1109/TAP.2023.3255640.

- [1.30] B. Glance, "A Fast Low-Loss Microstrip p-i-n Phase Shifter," in IEEE Transactions on Microwave Theory and Techniques, vol. 27, no. 1, pp. 14-16, Jan. 1979, doi: 10.1109/TMTT.1979.1129551.

- [1.31] H. Kondoh, "DC -50 GHz MMIC variable attenuator with a 30 dB dynamic range," 1988., IEEE MTT-S International Microwave Symposium Digest, New York, NY, USA, 1988, pp. 499-502 vol.1, doi: 10.1109/MWSYM.1988.22083.

- [1.32] C. F. Campbell and S. A. Brown, "A compact 5-bit phase-shifter MMIC for K-band satellite communication systems," in IEEE Transactions on Microwave Theory and Techniques, vol. 48, no. 12, pp. 2652-2656, Dec. 2000, doi: 10.1109/22.899026.

- [1.33] S. J. Kim and N. H. Myung, "A new active phase shifter using a vector sum method," in IEEE Microwave and Guided Wave Letters, vol. 10, no. 6, pp. 233-235, June 2000, doi: 10.1109/75.852426.

- [1.34] A. Asoodeh and M. Atarodi, "A Full 360° Vector-Sum Phase Shifter With Very Low RMS Phase Error Over a Wide Bandwidth," in IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 6, pp. 1626-1634, June 2012, doi: 10.1109/TMTT.2012.2189227.

- [1.35] K. -J. Koh and G. M. Rebeiz, "0.13-µm CMOS Phase Shifters for X-, Ku-, and K-Band Phased Arrays," in IEEE Journal of Solid-State Circuits, vol. 42, no. 11, pp. 2535-2546, Nov. 2007, doi: 10.1109/JSSC.2007.907225.

- [1.36] D. Coffing, E. Main, M. Randol and G. Szklarz, "A variable gain amplifier with 50-dB control range for 900-MHz applications," in IEEE Journal of Solid-State Circuits, vol. 37, no. 9, pp. 1169-1175, Sept. 2002, doi: 10.1109/JSSC.2002.801205.

- [1.37] Tae Wook Kim and Bonkee Kim, "A 78-dB gain range low power CMOS RF digitally programmable gain amplifier for mobile terrestrial D-TV tuner IC," in IEEE Microwave and Wireless Components Letters, vol. 16, no. 4, pp. 185-187, April 2006, doi: 10.1109/LMWC.2006.872130.

- [1.38] Q. Zhang et al., "A Ka-Band CMOS Phase-Invariant and Ultralow Gain Error Variable Gain Amplifier With Active Cross-Coupling Neutralization and Asymmetric Capacitor Techniques," in IEEE Transactions on Microwave Theory and Techniques, vol. 70, no. 1, pp. 85-100, Jan. 2022, doi: 10.1109/TMTT.2021.3125326.

- [1.39] B. Sadhu, et al., "7.2 A 28GHz 32-element phased-array transceiver IC with concurrent dual polarized beams and 1.4° beam-steering resolution for 5G communication," 2017 IEEE International Solid-State Circuits Conference (ISSCC), pp. 128-129, 2017, doi: 10.1109/ISSCC.2017.7870294.

- [1.40] K. Kibaroglu, M. Sayginer, and G. M. Rebeiz, "A low-cost scalable 32-element 28-GHz phased array transceiver for 5G communication links based on a 2 × 2 beamformer flip-chip unit cell," IEEE J. Solid-State Circuits, vol. 53, no. 5, pp. 1260-1274, 2018, doi: 10.1109/JSSC.2018.2791481.

- [1.41] T. Shimura et al., "Millimeter-wave TX phased array with phase adjusting function between transmitters for hybrid beamforming with interleaved subarrays," 2016 46th European Microwave Conference (EuMC), London, UK, 2016, pp. 1572-1575, doi: 10.1109/EuMC.2016.7824658.

- [1.42] O. Inac, D. Shin and G. M. Rebeiz, "A Phased Array RFIC With Built-In Self-Test Capabilities," in IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 1, pp. 139-148, Jan. 2012, doi: 10.1109/TMTT.2011.2170704.

# 2章 位相制御、振幅制御に関わるマイクロ波制御回路の原理

ここでは、図 1-1 内に示すマイクロ波モジュール内の移相器、位相検出器、可変利得増幅器といったマイクロ波制御回路の原理を示す。ここでは、シリコンデバイスで実現するマイクロ波制御回路の主要な方式として、移相器についてはベクトル合成型移相器、位相検出器についてはミクサをベースとしたアナログ位相検出器、可変利得増幅器についてはエミッタ接地回路、ベース接地回路を用いたものについて示す。

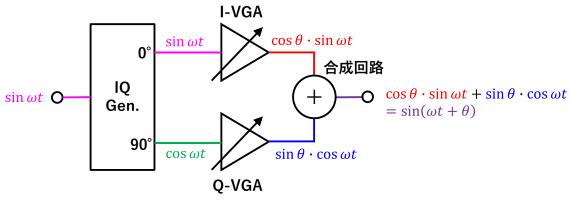

## 2.1. 移相器

移相器は様々な種類のものが提案されており、ベクトル合成型移相器、LC 回路を用いたもの、APN(All Pass Network)型、実時間遅延を用いたもの、反射型などがある。一般に、シリコン技術を使用したベクトル合成型移相器は、シリコンプロセスにおいて容易に実装できるディジタル回路を用いた高い振幅設定分解能を有する可変利得増幅器の適用による高い移相量設定分解能、I/Q(In-phase/Quadrature)誤差の低い I/Q 生成器による低移相量誤差、能動回路による正の通過振幅、インダクタを用いないことによる小型な実装といった特徴を有するため、大規模な AESA システムに適した方式となっている[2.1]-[2.13]。図 2-1 にベクトル合成型移相器(VSPS)の構成を示す。VSPS は I/Q 生成器(IQ Gen.)、2 つの可変利得増幅器 I-VGA、Q-VGA と合成回路(+)からなる。入力信号 $\sin \omega t$ は、I/Q生成器によってそれぞれ振幅が等しく位相が 90°異なる 0°(I):  $\sin \omega t$ と、90°(Q):  $\cos \omega t$ の 2 つの直交信号に分配される。それぞれの信号は、I-VGA、Q-VGA において移相したい角度 $\theta$ に対応する $\cos \theta$ と $\sin \theta$ の振幅の重みづけが行われ、 $\cos \theta$ ・ $\sin \omega t$ 、 $\sin \theta$ ・ $\cos \omega t$ となる。その後、合成器によって 2 つの信号は合成され $\sin(\omega t + \theta)$ となり、入力信号 $\sin \omega t$ に対し $\theta$ 移相した出力信号を得る。I/Q生成器には抵抗と容量の受動素子で構成されるポリフェーズフィルタが一般的に用いられる[2.14]-[2.16]。VGA の詳細は 2.3 節で示す。

図 2-1 ベクトル合成型移相器(VSPS)の構成

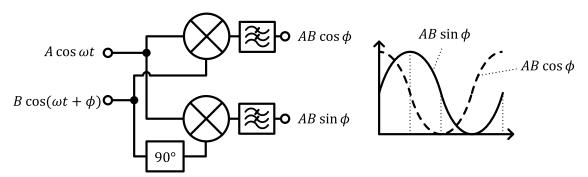

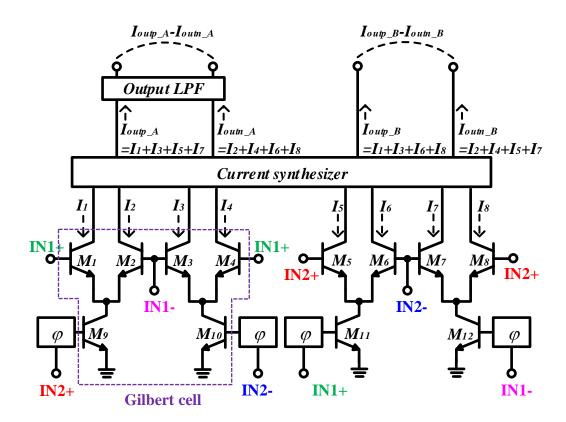

#### 2.2. 位相検出器

高周波信号の位相検出器は、高周波動作に対応するためミクサをベースとしたアナログ位相検出器が広く用いられている [2.17]-[2.22]。ミクサをベースとしたアナログ位相検出器の構成を図 2-2 に示す。本位相検出器は、2 つの入力信号 $A\cos\omega t$ と $B\cos(\omega t + \phi)$ の位相差 $\phi$ に応じた直流の電圧を出力する。ミクサは二つの入力信号の積を出力するため、上側のミクサの出力信号は以下の式で表される。

$$A\cos\omega t \times B\cos(\omega t + \phi) = \frac{AB}{2} \{\cos(\phi) + \cos(2\omega t + \phi)\}$$

(2-1)

上式の第二項は出力に設置した LPF によって抑圧されるため、第一項のみが出力される。第一項は、二つの信号の位相差 $\phi$ に対し余弦に比例する電圧 $(\cos\phi)$ となる。一方、下側のミクサは片方の入力に 90°移相器(90°)を設置されており、入力される 2 つの信号の位相差の正弦に比例する電圧 $(\sin\phi)$ を出力する。 2 つの出力の逆正接をとることで、検出位相差 $\phi_d$ を求めることが可能となる。本構成は 90°移相器の通過利得の影響によって位相差の正弦に比例する電圧 $(\sin\phi)$ が変動し検出誤差となる。

$$\phi_d = \tan^{-1} \left( \frac{\sin \phi}{\cos \phi} \right) \tag{2-2}$$

図 2-2 ミクサをベースとしたアナログ位相検出器の構成

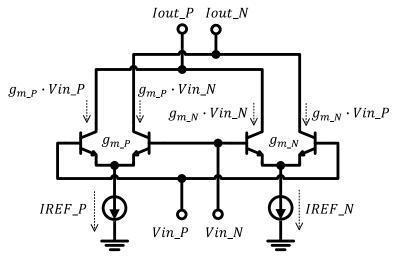

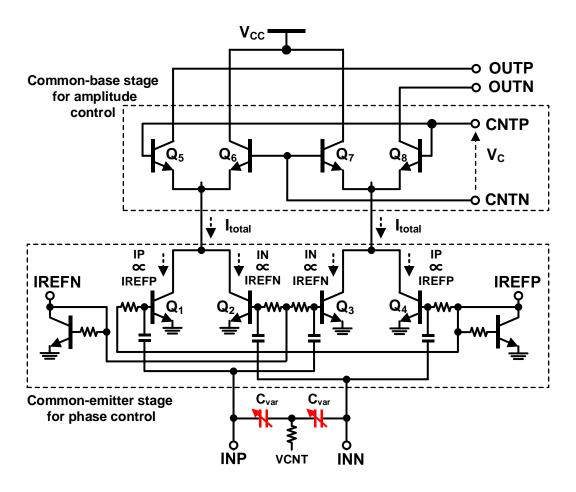

#### 2.3. 可変利得増幅器

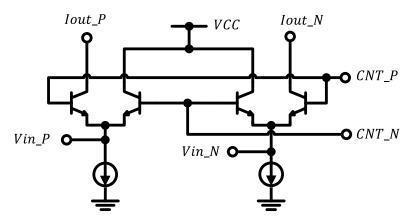

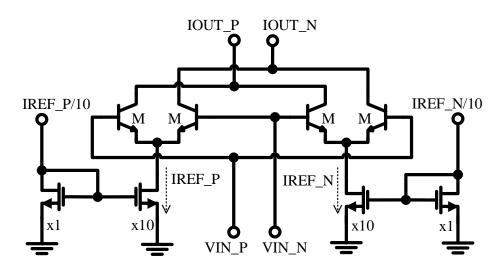

シリコン半導体内においてよく用いられる可変利得増幅器としては、エミッタ接地回路を用いたコモンエミッタ型 VGA と、ゲート接地回路を用いたコモンゲート型 VGA がある [2.23]-[2.26]。図 2-3 に完全差動型のコモンエミッタ型 VGA の回路構成を示す。コモンエミッタ型 VGA は、エミッタ接地差動対を 2 つ用いて、2 つの出力を逆相合成する構成をとる。それぞれのテール電流 $IREF_P$ 、 $IREF_N$ の大きさを調整し正相信号と逆相信号の振幅調整した後に合成することで可変利得機能を実現する。入力電圧に対する出力電流の利得  $G_{VGACE}$ は以下の式で表され、トランジスタのトランスコンダクタンスの差に比例する。

$$G_{VGA\_CE} = \frac{\Delta Iout}{\Delta Vin} = \frac{Iout\_P - Iout\_N}{Vin\_P - Vin\_N} = g_{m\_P} - g_{m\_N}$$

(2-3)

トランスコンダクタンスは、以下のようにトランジスタのテール電流 $IREF_P$ 、 $IREF_N$ に比例する。

$$g_{m,P} \propto IREF_P, \quad g_{m,N} \propto IREF_N$$

(2-4)

双方のトランジスタのテール電流IREF\_P、IREF\_Nが等しいときに、正相と逆相が全く等しい振幅となり、出力は打ち消されゼロとなる。このように、コモンエミッタ型 VGA はテール電流で利得制御が可能となるため、シリコンプロセスにおいて容易に実装できるディジタル回路を用いた高い振幅設定分解能を実現することが可能となる。

図 2-4 に完全差動型のコモンベース型 VGA の回路構成を示す。コモンベース型 VGA は、2 つのベース接地の差動対を用いる。差動対のベース端子制御電圧 $CNT_P$ 、 $CNT_N$ の差分電  $EV_C = CNT_P - CNT_N$ で、出力電流 $Iout_P$ 、 $Iout_N$ を制御することにより可変利得機能を実現する。ここで、入力電圧に対する出力電流の利得 $G_{VGACB}$ は以下の式で表される。

$$G_{VGA\_CB} = \frac{\exp\left(\frac{V_c}{V_t}\right)}{\exp\left(\frac{V_c}{V_t}\right) + 1}$$

(2-5)

ここで、 $V_t$ は熱電圧( $=26\,\text{mV@}300\,\text{K}$ )である。 $V_c=0$  のときに利得は 1/2 (-6 dB)となる。利得の特性は $V_c$ に対し出力が $10\cdot log(V_c)$ で変化するため、制御性が良いという特徴を有する [2.27]。コモンエミッタ型 VGA とコモンベース型 VGA の両者を組み合わせことで移相機能と可変利得機能の二つを一つの回路で実現する可変利得移相器という回路構成も提案されている[2.28]。

図 2-3 コモンエミッタ型 VGA の回路構成

図 2-4 コモンベース型 VGA の回路構成

# 2.4. 参考文献

- [2.1] Kalyoncu, E. Ozeren, and A. Burak, "A Phase-Calibration Method for Vector-Sum Phase Shifters Using a Self-Generated LUT," IEEE Tran. Circuits Syst. I, Reg. papers, vol. 66, no. 4, pp. 1632-1642, Apr. 2019.

- [2.2] J. Pang et al., "A 28-GHz CMOS Phased-Array Transceiver Based on LO Phase-Shifting Architecture with Gain Invariant Phase Tuning for 5G New Radio," IEEE J. Solid-state Circuits, vol. 54, no. 5, pp. 1228-1242, May 2019.

- [2.3] I. Kalyoncua. Burak, M. Kaynak, and Y. Gurbuz, "A 26-GHz Vector Modulator in 130-nm SiGe BiCMOS Achieving Monotonic 10-b Phase Resolution Without Calibration," in Proc. IEEE RFIC, June 2019.

- [2.4] Y. Wang et al., "A 39GHz 64-Element Phased-Array CMOS Transceiver with Built-in Calibration for Large-Array 5G NR," in Proc. IEEE RFIC, June 2019.

- [2.5] B. Sadhu et al., "A 28-GHz 32-Element TRX Phased-Array IC With Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications," IEEE J. Solid-state Circuits, vol. 52, no. 12, pp.3373-3391, Dec. 2017.

- [2.6] H. Zijie, K. Mouthaan, "A 0.5–6 GHz 360° vector-sum phase shifter in 0.13-  $\mu$  m CMOS," in Proc. IEEE IMS, June 2014.

- [2.7] M. Mohsenpour, C. E. Saavedra, "Variable 360° Vector-Sum Phase Shifter with Coarse and Fine Vector Scaling," IEEE Trans. Microw. Theory and Techn., vol. 64, no. 7, pp. 2113-2120, July 2016.

- [2.8] T. Yan, W. Lin, and C. Kuo, "A 0.75-2.67 GHz 5-bit Vector-Sum Phase Shifter," in Proc. European Microwave Integrated Circuits Conference, Oct. 2013, pp. 196 199.

- [2.9] E. V. Balashov, I. A. Rumyancev, "A Fully Integrated 6-bit Vector-Sum Phase Shifter in 0.18 · m CMOS," in Proc. 2015 International Siberian Conference on Control and Communications, May 2015.

- [2.10] Y. Xu, J. Xia, S. Boumaiza, "A 0.6-2.8GHz CMOS RF Vector Multiplier with Low RMS Magnitude and Phase Errors and High P1dB," in Proc. IEEE IMS, June 2017, pp. 2015-2017.

- [2.11] J. Xia, Y. Xu, H. Huang, S. Boumaiza, "A 0.1-5.7 GHz CMOS Phase Shifter with 0.27dB/1.8 o RMS Magnitude/Phase Errors and Enhanced Linearity," in Proc. IEEE 19th Topical Meeting on Silicon Monolithic Integrated Circuits in RF System (SiRF), Jan. 2019, pp. 1-3.

- [2.12] A. Asoodeh and M. Atarodi, "A Full 360 Vector-Sum Phase Shifter with Very Low

- RMS Phase Error Over a Wide Bandwidth," IEEE Trans. Microw. Theory and Techn., vol. 60, pp. 1626-1634, June 2012.

- [2.13] F. Albar, A. Mortazawi, "A Frequency Tunable 360 o Analog CMOS Phase Shifter with an Adjustable Amplitude," IEEE Tran. Circuits Syst. II: Exp. Briefs, vol. 64, no. 12, pp. 1427-1431, Dec. 2017.

- [2.14] A. Asoodeh and S. Mirabbasi, "On the Design of nth-Order Polyphase All-Pass Filters," IEEE Tran. Circuits Syst. I, Reg. Papers, vol. 66, no. 1, pp. 133146, Jan. 2019.

- [2.15] J. Kaukovuori, K. Stadius, J. Ryynanen, and K. Halonen, "Analysis and design of passive polyphase filters," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 10, pp. 30233037, Nov. 2008.

- [2.16] M. Momeni and M. Moezzi, "A low loss and area efficient RC passive poly phase filter for monolithic GHz vector-sum circuits," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 66, no. 7, pp. 11341138, Jul. 2019.

- [2.17] L. Wua. Li, and H. C. Luong, "4-Path 42.8-to-49.5 GHz LO Generation," IEEE J. Solid-state Circuits, vol. 48, no. 10, pp. 2309–2322, Oct. 2013.

- [2.18] A. Hirai, K. Tsutsumi, Y. Takahashi, H. Nakamizo, K. Tajima, E. Taniguchi, M. Hieda, and M. Nakayama, "Fast and Highly Accurate RF Phase Detector with Analog Integrator for APAA System," in Proc. APMC, pp. 1–3, Nov. 2013.

- [2.19] M. Dwyer, A. Day, and D. Weide "Enhanced phase detector using nonlinear transmission lines," in Proc. RWS, Jan. 2019.

- [2.20] C. Tang and Q. Xue, "S-Band Full 360° High Precision Phase Detector," in Proc. APMC, pp. 97–99, Dec. 2012.

- [2.21] B. Perez, V. A. Arana, J. Perez-Mato, and F. Cabrera, "360° Phase Detector Cell for Measurement Systems Based on Switched Dual Multipliers," IEEE Trans. Microw. Theory Techn., vol. 27, no. 5, pp. 503–505, May 2017.

- [2.22] B. Philippe and P. Reynaert, "A Quadrature Phase Detector in 28nm CMOS for Differential mm-Wave Sensing Applications using Dielectric Waveguides," in Proc. IEEE ESSCIRC, pp. 114–117, Sep. 2018.

- [2.23] Q. Zhang, C. Zhao, Y. Yu, H. Liu, Y. Wu and K. Kang, "A Ka-band CMOS variable gain amplifier with high gain resolution and low phase variation," 2020 IEEE Asia-Pacific Microwave Conference (APMC), pp. 275-277, 2020, doi: 10.1109/APMC47863.2020.9331365.

- [2.24] S. Lee, J. Park, and S. Hong, "A Ka-band phase-compensated variable-gain CMOS low-noise amplifier," IEEE Microw. Wirel. Compon. Lett., vol. 29, no. 2, pp. 131-133, 2019, doi: 10.1109/LMWC.2018.2887335.

- [2.25] G. H. Park, J. K. Kwon, D. M. Kang, and C. S. Park, "A 60-GHz variable gain amplifier with phase-compensated variable attenuator," 2021 IEEE 20th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), pp. 44-46, 2021, doi: 10.1109/SiRF51851.2021.9383343.

- [2.26] D. Siao, J. Kao, and H. Wang, "A 60 GHz low phase variation variable gain amplifier in 65 nm CMOS," IEEE Microw. Wirel. Compon. Lett., vol. 24, no. 7, pp. 457-459, 2014, doi: 10.1109/LMWC.2014.2316253.

- [2.27] D. Coffing, E. Main, M. Randol, and G. Szklarz, "A variable gain amplifier with 50-dB control range for 900-MHz applications," IEEE J. Solid-State Circuits, vol. 37, no. 9, pp. 1169-1175,2002, doi: 10.1109/JSSC.2002.801205.

- [2.28] S. Wang, J. Park, and S. Hong, "A K-band variable-gain phase shifter based on Gilbert-cell vector synthesizer with RC–RL poly-phase filter," IEEE Microw. Wirel. Compon. Lett., vol. 31, no. 4, pp. 393-396, 2021, doi: 10.1109/LMWC.2021.3056881.

# 3章 g<sub>m</sub>-C ポリフェーズフィルタを用いた広帯域な移相器

## 3.1. まえがき

移相器は、正確なビーム制御機能を実現するための重要な回路の一つであり、AESAのビーム制御高精度化のためには移相器の高精度化、つまり、設定移相量に対して低い誤差での移相量制御が求められる。また、近年 AESA の高機能化、高性能化のため、より広い周波数帯域での低移相量誤差を実現が求められている[3.1]-[3.5]。さらに、AESAの大規模化に伴い、より小さなチップサイズでの実現や汎用的な半導体プロセスであるシリコンプロセスによる低コスト化、低消費電力化の要求も増大している[3.6]-[3.9]。

本章では、広帯域に低移相量誤差性能を実現する移相技術として、ベクトル合成型移相器 [3.10]-[3.13]内の I/Q 生成器に、新しい回路構成である  $g_m$ -C ポリフェーズフィルタ (PPF) を適用した移相器の回路構成、およびその設計法を提案する。 $g_m$ -C PPF は、従来の I/Q 生成器である RC-PPF [3.14]-[3.16]の抵抗 R の代わりにトランジスタのトランスコンダクタンス  $g_m$  を用いることで、従来方式で生じていた比帯域と通過損失のトレードオフの関係を解決し、広い周波数帯域における低移相量誤差を実現する。また、RC-PPF において受動デバイスのみで構成されることで生じていた通過損失を、トランジスタのトランスコンダクタンスを利用することにより通過利得に変えることができる。それにより、I/Q 生成器で発生する通過損失を補償する増幅器を削除し、低消費電力化、小型化も合わせて実現する。提案する  $g_m$ -C PPF を含む移相器の設計法を導出したのちに、提案する移相器を S 帯(2-4 GHz)で試作した結果について述べ、本回路構成と設計法の有効性を示す。

#### 3.2. 移相器の回路構成と設計法

#### 3.2.1. 従来回路の問題点

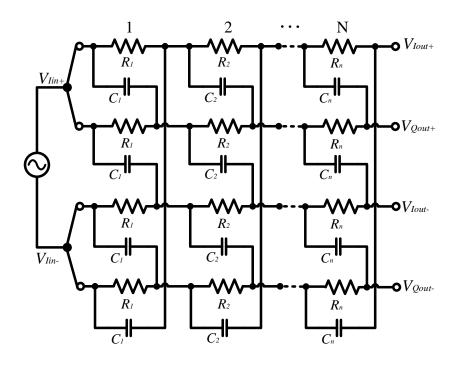

広帯域に低移相量誤差な VSPS を実現する方法として主に 2 つのアプローチがある。一つ目の手法は、ディジタルによる移相性能のキャリブレーションである[3.1][3.4]。このアプローチでは、I/Q 生成器や VGA で生じた誤差を、出力に配置した誤差検出回路とディジタル処理を用いて最適化された I/Q 設定で制御する。この手法では低い移相量誤差を実現できるが、検出と制御のための回路が必要となりチップ面積が大きくなる。また、IC 外部制御ユニットが必要になる場合 AESA の小型化、低コスト化が困難となる。二つ目のアプローチ方法は、I/Q 誤差の低い I/Q 生成器の実現である[3.13]-[3.21]。VSPS に I/Q 生成器を小型に実装する方法の一つとして、RC-PPF がある[3.14]。図 3-1 に RC-PPF の回路構成を示す。1 段の RC-PPF の I と Q の出力の比は以下のようになる。

$$I/Q_{RC\ PPF(n=1)} = \frac{V_{Iout+} - V_{Iout-}}{V_{Qout+} - V_{Qout-}} = \frac{1 - \frac{j\omega}{\omega_{p,1\ (RC\ PPF)}}}{1 + \frac{j\omega}{\omega_{p,1\ (RC\ PPF)}}}$$

(3-1)

ここで、

$$\omega_{p,n(RC\ PPF)} = \frac{1}{R_n C_n} \tag{3-2}$$

である。2段のRC-PPFのIとQの出力の比は以下のようになる。

$$I/Q_{RC\;PPF(n=2)} = \frac{1 - j\omega\left(\frac{1}{\omega_{p,1(RC\;PPF)}} + \frac{1}{\omega_{p,2(RC\;PPF)}}\right) + \omega^2 \frac{1}{\omega_{p,1(RC\;PPF)}\omega_{p,2(RC\;PPF)}}}{1 + j\omega\left(\frac{1}{\omega_{p,1(RC\;PPF)}} + \frac{1}{\omega_{p,2(RC\;PPF)}}\right) + \omega^2 \frac{1}{\omega_{p,1(RC\;PPF)}\omega_{p,2(RC\;PPF)}}}$$

(3-3)

(3-1)式、(3-3)式より I/Q 振幅比は常に 1 となる。また、I と Q の位相差は、角周波数  $\omega = \omega_{p,1(RC\ PPF)} = \omega_{p,2(RC\ PPF)} = 1/R_nC_n$ において 90°となる。RC-PPF は抵抗と容量で構成できるため小型な面積を実現できる。また、段数を増やすことで I/Q 誤差の小さい周波数帯域幅が増加するが、挿入損失が増加するため挿入損失と I/Q 誤差の比帯域幅の関係がトレードオフとなる。つまり、広い帯域を実現する場合には通過損失が増大し、その通過損失を補償するための増幅回路が必要となり消費電力が増加するといった問題がある[3.15]。

図 3-1 RC-PPF の回路構成

# 3.2.2. 提案する回路構成と動作原理・設計法

#### 3.2.2.1. g<sub>m</sub>-C PPF の周波数特性と I/Q 誤差

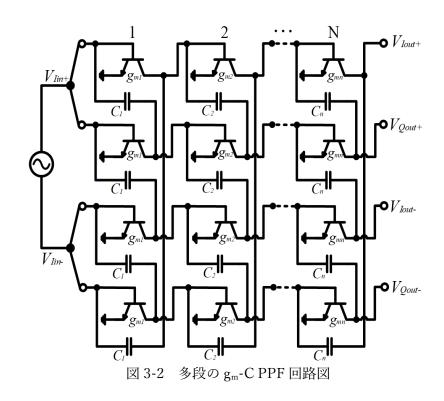

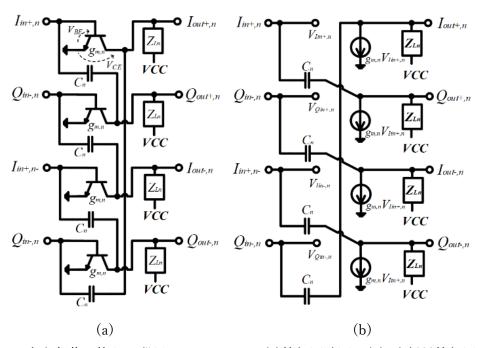

図 3-2 に提案する多段の  $g_m$ -C PPF の回路図を示す。 $g_m$ -C PPF は、従来の RC-PPF の抵抗の代わりにトランジスタを用いる。インピーダンス  $Z_{Ln}$  の出力負荷を伴う n 段目の  $g_m$ -C PPF の回路図と小信号等価回路図をそれぞれ図 3-3(a)、(b)に示す。 $g_m$ -C PPF の出力電圧は、小信号等価回路から計算できる。I 出力信号 $\Delta V_{Iout,n}(\omega)$ と Q 出力信号 $\Delta V_{Qout,n}(\omega)$ の差動電圧は、次のように与えられる[3.26]。

$$\Delta V_{lout,n}(\omega) = V_{lout+,n}(\omega) - V_{lout-,n}(\omega)$$

$$= \frac{Z_{Ln}}{\frac{1}{a_{m,n}} + Z_{Ln} \cdot \frac{j\omega C_n}{a_{m,n}}} \left( -\Delta V_{lin,n}(\omega) - j\frac{\omega C_n}{g_{m,n}} \Delta V_{Qin,n}(\omega) \right), \tag{3-4a}$$

$$\Delta V_{Qout,n}(\omega) = V_{Qout+n}(\omega) - V_{Qout-n}(\omega)$$

$$= \frac{Z_{Ln}}{\frac{1}{g_{mn}} + Z_{Ln} \cdot \frac{j\omega C_n}{g_{mn}}} \left( -\Delta V_{Qin,n}(\omega) + j \frac{\omega C_n}{g_{m,n}} \Delta V_{Iin,n}(\omega) \right). \tag{3-4b}$$

ここで、 $\omega$ は角周波数、 $g_{m,n}$ はトランジスタのトランスコンダクタンス、 $C_n$ は容量値、 $Z_{Ln}$ は n 段目の  $g_m$ -C PPF の出力負荷インピーダンスである。(3-4)式は、次のような行列で表すことができる。

$$\begin{bmatrix} \Delta V_{lout,n}(\omega) \\ \Delta V_{Qout,n}(\omega) \end{bmatrix} = \frac{Z_{Ln}}{\frac{1}{g_{mn}} + Z_{Ln} \frac{j\omega}{\omega_{nn}}} \begin{bmatrix} -1 & -j\omega/\omega_{p,n} \\ j\omega/\omega_{p,n} & -1 \end{bmatrix} \begin{bmatrix} \Delta V_{lin,n}(\omega) \\ \Delta V_{Qin,n}(\omega) \end{bmatrix}$$

(3-5)

ここで、

$$\omega_{p,n} = \frac{g_{m,n}}{C_m} \tag{3-6}$$

である。(3-6)式は、 $g_{m,n}$ を変化させることで、 $\omega_{p,n}$ を変化できることを示している。 $g_{m,n}$ はトランジスタの電流によって変化させることが可能であり、電流を制御することで $\omega_{p,n}$ の制御が可能となる。

入力信号が理想的な差動信号( $V_{lin+}=-V_{lin-}$ )であり、I/Q 入力端子が短絡されていると仮定すると、1 段(N=1)の  $g_m$ -C PPF の伝達関数 $H_{1-stg,I}(\omega)$ と $H_{1-stg,Q}(\omega)$ は、次のように計算される。

$$\begin{cases} H_{1-stg,I}(\omega) = \frac{\Delta V_{lout}(\omega)}{\Delta V_{in}(\omega)} = \frac{Z_{L1}}{\frac{1}{g_{m,1}} + Z_{L1} \cdot \frac{j\omega}{\omega_{p,1}}} (-1 - \frac{j\omega}{\omega_{p,1}}) \\ H_{1-stg,Q}(\omega) = \frac{\Delta V_{Qout}(\omega)}{\Delta V_{in}(\omega)} = \frac{Z_{L1}}{\frac{1}{g_{m,1}} + Z_{L1} \cdot \frac{j\omega}{\omega_{p,1}}} (-1 + \frac{j\omega}{\omega_{p,1}}) \end{cases}$$

(3-7)

IとQの出力の比は以下のようになる。

$$\frac{H_{1-stg,I}(\omega)}{H_{1-stg,Q}(\omega)} = \frac{1 + \frac{j\omega}{\omega_{p,1}}}{1 - \frac{j\omega}{\omega_{p,1}}}$$

(3-8)

(3-8)式より、I/Qの振幅比と位相差は以下のように計算される。

$$\left| \frac{H_{1-stg,I}(\omega)}{H_{1-stg,Q}(\omega)} \right| = 1, \tag{3-9a}$$

$$\emptyset_{1-stg} = \angle \frac{H_{1-stg,I}(\omega)}{H_{1-stg,Q}(\omega)} = \tan^{-1} \left( \frac{\frac{2\omega}{\omega_{p,1}}}{1 - \left(\frac{\omega}{\omega_{p,1}}\right)^2} \right). \tag{3-9b}$$

(3-9)式より、I/Q 振幅比は、トランスコンダクタンス、周波数範囲、静電容量、負荷インピーダンスに依存せず常に 1 となる。一方、I と Q の位相差は、角周波数 $\omega=\omega_{p,1}=g_{m,1}/C_1$  において 90° となる。(3-8)式と(3-9)式より、 $g_m$ -C PPF の伝達関数は RC-PPF[3.15]と同等であることがわかる。(3-8)式と(3-1)式を比較すると、1 段の RC-PPF 伝達関数の抵抗 R が、 $g_m$ -C PPF において $1/g_{m,1}$ に置き換わっていることがわかる。 $g_m$ -C PPF は、従来の RC-PPF と同様に直列段数を増やすことによって、より広い比帯域幅を実現することが可能となる。 2 段(N=2)  $g_m$ -C PPF の I/Q の伝達関数は(3-5)式から導出され、次のように与えられる。

$$\begin{cases} H_{2-stg,I}(\omega) = \frac{\Delta V_{Iout,2}(\omega)}{\Delta V_{in}(\omega)} = \frac{Z_{L1}Z_{L2} \left\{ 1 + j\omega \left( \frac{1}{\omega_{p,1}} + \frac{1}{\omega_{p,2}} \right) + \omega^2 \frac{1}{\omega_{p,1}\omega_{p,2}} \right\} \\ \left( \frac{1}{g_{m,1}} + Z_{L1} \cdot \frac{j\omega}{\omega_{p,1}} \right) \left( \frac{1}{g_{m,2}} + Z_{L2} \cdot \frac{j\omega}{\omega_{p,2}} \right) \\ H_{2-stg,Q}(\omega) = \frac{\Delta V_{Qout,2}(\omega)}{\Delta V_{in}(\omega)} = \frac{Z_{L1}Z_{L2} \left\{ 1 - j\omega \left( \frac{1}{\omega_{p,1}} + \frac{1}{\omega_{p,2}} \right) + \omega^2 \frac{1}{\omega_{p,1}\omega_{p,2}} \right\} \\ \left( \frac{1}{g_{m,1}} + Z_{L1} \cdot \frac{j\omega}{\omega_{p,1}} \right) \left( \frac{1}{g_{m,2}} + Z_{L2} \cdot \frac{j\omega}{\omega_{p,2}} \right) \end{cases}$$

(3-10)

IとQの出力比は以下のようになる。

$$\frac{H_{2-stg,I}(\omega)}{H_{2-stg,Q}(\omega)} = \frac{1 + j\omega \left(\frac{1}{\omega_{p,1}} + \frac{1}{\omega_{p,2}}\right) + \omega^2 \frac{1}{\omega_{p,1}\omega_{p,2}}}{1 - j\omega \left(\frac{1}{\omega_{p,1}} + \frac{1}{\omega_{p,2}}\right) + \omega^2 \frac{1}{\omega_{p,1}\omega_{p,2}}}$$

(3-11)

(3-11)式と(3-3)式を比較すると、2 段の RC-PPF 伝達関数の抵抗 R も  $g_m$ -C PPF において $1/g_{mn}$ に置き換えられることがわかる。ここで、

$$\omega_{p,n} = \frac{g_{m,n}}{C_n} \tag{3-12}$$

となる。 $\omega_p = \omega_{p,1} = \omega_{p,2}$ とすると、I/Q の振幅比と位相差は以下のように計算される。

$$\left| \frac{H_{2-stg,I}(\omega)}{H_{2-stg,Q}(\omega)} \right| = 1, \tag{3-13a}$$

$$\emptyset_{2-stg} = \angle \frac{H_{2-stg,I}(\omega)}{H_{2-stg,Q}(\omega)} = \tan^{-1} \left( \frac{\frac{4\omega}{\omega_p} (1 + \frac{\omega^2}{\omega_p^2})}{\left(1 - \frac{\omega^2}{\omega_p^2}\right)^2} \right).$$

(3-13b)

位相傾きは以下のように計算される。

$$\left. \frac{\partial \phi_{2-stg}}{\partial \omega} \right|_{\omega = \omega_p} = \frac{4\omega_p^3 - 4\omega^2 \omega_p}{\omega_p^4 + 6\omega^2 \omega_p^2 + \omega^4} \right|_{\omega = \omega_p} = 0 \tag{3-14}$$

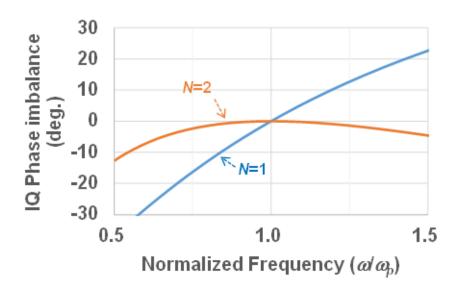

(3-13)式、(3-14)式より 2 段の  $g_m$ -C PPF がより広帯域に I/Q の位相バランスを実現できることがわかる。(3-9)式と(3-13)式を用いて計算した 1 段(N=1)と 2 段(N=2)の  $g_m$ -C PPF の I/Q 位相誤差を図 3-4 に示す。周波数は $\omega_p$ で正規化している。I/Q 位相誤差は、VSPS の移相誤差と振幅誤差を引き起こすため、VSPS の比帯域幅を決定する。I/Q 位相誤差と VSPS

の比帯域幅については 3.2.2.4 節で説明する。

図 3-3 出力負荷を伴う n 段目の  $g_m$ -C PPF o(a)等価回路図、(b) 小信号等価回路図

図 3-4 1 段(N=1) と 2 段(N=2)の  $g_m$ -C PPF の I/Q 位相誤差

#### 3.2.2.2. g<sub>m</sub>-C PPF の電圧利得

1段の  $g_m$ -C PPF に関して、角周波数 $\omega_{p,1}$ における I/Q それぞれの伝達関数は以下のように表される。

$$H_{1-stg,I}(\omega_{p,1}) = \frac{1}{\frac{1}{g_{m,1}Z_{L1}} + j} (-1-j), \tag{3-15a}$$

$$H_{1-stg,Q}(\omega_{p,1}) = \frac{1}{\frac{1}{g_{m,1}Z_{L1}} - j} (-1+j). \tag{3-15b}$$

ここで $Z_{L1}$ が純抵抗Rの場合、 $\omega_{p,1}$ における電圧利得は以下のように表される。

$$\left| H_{1-stg,I}(\omega_{p,1}) \right| = \left| H_{1-stg,Q}(\omega_{p,1}) \right| = \frac{\sqrt{2}}{\sqrt{\frac{1}{\left(g_{m,1}R\right)^2} + 1}}$$

(3-16)

通過利得が正となる条件は以下となる。

$$g_{m,1}R > 1 (3-17)$$

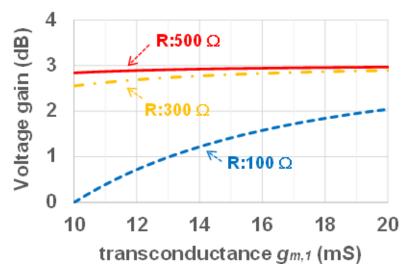

(3-16)式より、 $g_{m,1}R$ の値で電圧利得は変化し、 $g_{m,1}R>>1$  において  $g_m$ -C PPF の最大利得は 3 dB ( $\sqrt{2}$ )となる。図 3-5 に、(3-16)式によって計算された 1 段  $g_m$ -C PPF のトランスコンダクタンス $g_{m,1}$ に対する電圧利得依存性の例を示す。Rは  $100\Omega$ 、 $300\Omega$ 、 $500\Omega$ の 3 条件で、 $g_{m,1}$ は 10 mS $\sim$ 20 mS である。 $g_{m,1}$ は、(3-12)式に示すように所望周波数と容量によって決定される。より高いRを使用することで、 $g_{m,1}$ 依存性が減少する。一方、すべてのトランジスタは飽和領域( $V_{CE}>V_{BE}$ )で動作する必要があるため、Rの選択できる抵抗最大値はトランジスタの DC バイアス電圧によって制限される。また、過度に高い抵抗を使用すると、後段の VGA とのインピーダンス整合が困難となる。

図 3-5 1段 gm-C PPF のトランスコンダクタンスに対する電圧利得依存性の例

#### 3.2.2.3. g<sub>m</sub>-C PPF の周波数可変範囲と利得変動

$g_m$ -C PPF では、トランジスタのトランスコンダクタンス $g_{m,n}$ を変化させることで角周波数 $\omega_p$ を制御でき、これは  $g_m$ -C PPF の I/Q 誤差がゼロとなる周波数を変化させることで動作帯域を拡張し広帯域化できることを意味する。  $g_{m,n}$ 変化幅の最小値を $g_{m,n\_min}$ 、最大値を $g_{m,n\_max}$ とすると、周波数可変範囲 $FR_{tun}$ は以下のように表される。

$$FR_{tun.} = \frac{\omega_{p\_max} - \omega_{p\_min}}{(\omega_{p\_max} + \omega_{p\_min})/2} = \frac{2(g_{m,n\_max} - g_{m,n\_min})}{g_{m,n\_max} + g_{m,n\_min}}$$

(3-18)

バイポーラトランジスタを用いた差動対の場合は、 $g_{m,n}$ は直流電流IREFに変化し以下にように表される。

$$g_{m,n} = IREF_{m,n}/\alpha V_t \tag{3-19}$$

ここで $V_t$ は熱電圧、 $\alpha$ は半導体のプロセステクノロジーによって決まる値である。(3-18)式、(3-19)式より、バイポーラを用いたとき周波数可変範囲 $FR_{tun.}$ は以下のようになる。

$$FR_{tun.} = \frac{2\left(IREF_{m,n\_max} - IREF_{m,n\_min}\right)}{IREF_{m,n\_max} + IREF_{m,n\_min}}$$

(3-20)

このように、 $g_m$ -C PPF は直流電流を変化させることで利用可能な周波数範囲を拡張することが可能となる。各トランジスタは直流バイアス電圧が $V_{CE}>V_{BE}$ となる飽和領域での条件で電圧設定する必要があるため、最大の設定可能な直流電流 $IREF_{mn\ max}$ は以下で表される。

$$IREF_{m,n\_max} < \frac{VCC - V_{BE}}{R} \tag{3-21}$$

ここで負荷 $Z_{Ln}$ は純抵抗Rとしている。(3-19)式と(3-21)式より、設定可能な最大トランスコンダクタンス $g_{mn\ av\ max}$ は以下となる。

$$g_{m,n\_av\_max} = \frac{VCC - V_{BE}}{\alpha V_{+}R}$$

(3-22)

一方、設定可能な最小トランスコンダクタンス $g_{m,n\_min}$ は利得変動量から決定される。(3-16)式より、 $g_{m,1}$ 変化にともなう利得変動 $\Delta G$ は以下の式で表される。

$$\Delta G = \frac{\sqrt{2}}{\sqrt{\frac{1}{(g_{m,1\_max} \cdot R)^2} + 1}} = \frac{\sqrt{\frac{1}{(g_{m,1\_min} \cdot R)^2} + 1}}{\sqrt{\frac{1}{(g_{m,1\_min} \cdot R)^2} + 1}} = \frac{\sqrt{\frac{1}{(g_{m,1\_min} \cdot R)^2} + 1}}{\sqrt{\frac{1}{(g_{m,1\_max} \cdot R)^2} + 1}}$$

(3-23)

(3-18)式と(3-23)式より、設定可能な最大周波数範囲 $FR_{tun\_av\_max}$ は、利得変動量 $\Delta G$ を用いて以下のように表される。

$$FR_{tun\_av\_max} = \frac{2(\sqrt{\Delta G^2 + (\Delta G^2 - 1) \cdot g_{m,n\_av\_max}^2 \cdot R^2} - 1)}{\sqrt{\Delta G^2 + (\Delta G^2 - 1) \cdot g_{m,n\_av\_max}^2 \cdot R^2} + 1}$$

(3-24)

(3-24)式より、 $g_{m,n\_av\_max}$ と負荷抵抗R、利得変動量 $\Delta G$ が設定可能な最大周波数範囲  $FR_{tun\_av\_max}$ を決定することがわかる。バイポーラトランジスタを用いたときの $FR_{tun\_av\_max}$ は、(3-22)式と(3-24)式から以下のように計算される。

$$FR_{tun\_av\_max} = \frac{2\left(\sqrt{\Delta G^2 + (\Delta G^2 - 1) \cdot \left(\frac{VCC - V_{BE}}{\alpha V_t}\right)^2} - 1\right)}{\sqrt{\Delta G^2 + (\Delta G^2 - 1) \cdot \left(\frac{VCC - V_{BE}}{\alpha V_t}\right)^2} + 1}$$

(3-25)

(3-25)式より、 $FR_{tun\_av\_max}$ は電源電圧 VCC とベース端子電圧 $V_{BE}$ 、また、半導体のプロセステクノロジーで決まり、より高い VCC と低い $V_{BE}$ を適用することで、より広い $FR_{tun\_av\_max}$ を実現できる。

#### 3.2.2.4. gm-C PPF を適用した移相器の移相量誤差と振幅誤差

$g_m$ -C PPF の I/Q 誤差 $\theta_e$ による VSPS の移相量誤差 $\varphi_{err,i}$ [3.16]と振幅誤差 $A_{err,i}$ は以下のように表される。

$$\varphi_{err,i} = \tan^{-1} \left( \frac{\cos(\varphi_i - \theta_e) - \cos(\varphi_i)}{\sin(\varphi_i - \theta_e) + \cos(\varphi_i)\cot(\varphi_i)} \right), \tag{3-26a}$$

$$A_{err,i} = \sqrt{1 - 2\sin\varphi_i\cos\varphi_i\sin\theta_e} \,, \ i = 1 - 2^n. \tag{3-26b}$$

ここで、 $\varphi_i$ は理想移相量である。m-bit 移相器における、 $\mathsf{g_m}$ -C PPF の  $\mathrm{I/Q}$  誤差に起因する RMS 移相量誤差 $\varphi_{rms}$ と RMS 振幅誤差 $A_{rms}$ は以下のように表される。

$$\varphi_{rms} = \sqrt{\frac{\sum_{i=0}^{2^{m}} \varphi_{err,i}^{2}}{2^{m}}},$$

(3-27a)

$$A_{rms} = \sqrt{\frac{\sum_{i=0}^{2m} A_{err,i}^2}{2^m}}. (3-27b)$$

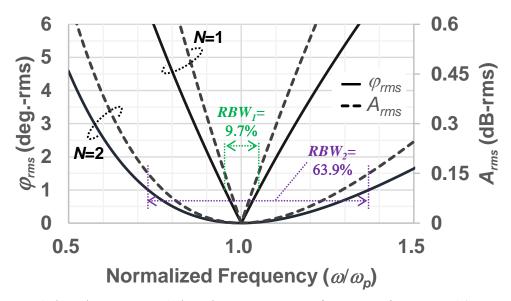

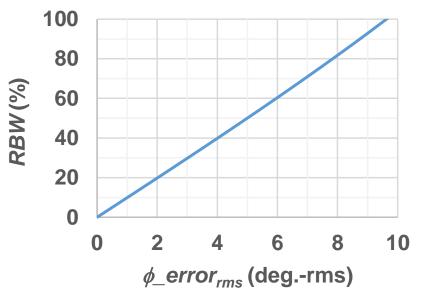

図 3-6 に、(3-26)式、(3-27)式を用いて計算した 1 段(N=1)、および 2 段(N=2)の  $g_m$ -C PPF を適用した場合の 6-bit 移相器の RMS 移相量誤差 $\varphi_{rms}$ と RMS 振幅誤差 $A_{rms}$ を示す。 周波数は $\omega_p$ で規格化している。 $g_m$ -C PPF の I/Q 誤差が VSPS の一定以下の移相量誤差と振幅誤差を実現する周波数比帯域幅 RBW を決定する。例えば、 $1^o$ -rms と 0.15 dB-rms 以下の RMS 移相量誤差、振幅誤差を実現するためには、1 段  $g_m$ -C PPF の場合の RBW $_1$  は 9.7%となる。2 段  $g_m$ -C PPF を用いた場合の RBW $_2$  は 63.9%となる。

g<sub>m</sub>-C PPF を用いた場合、RBW に追加し 3.2.2.3 節で示した周波数可変機能によって、周波数範囲を拡張することが可能となる。利用可能な最大周波数範囲 TBW は以下の式で表される。

$$TBW = RBW_n + FR_{tun}. (3-28)$$

必要となる瞬時周波数帯域が 9.7%で、利用可能な最大周波数範囲が 29.3 %以下の場合、 1 段 g<sub>m</sub>-C PPF が適用可能となる。一方、瞬時周波数帯域が 9.7 %を超える場合、2 段 g<sub>m</sub>-C PPF が必要となる。

図 3-6 1 段(N=1)、および 2 段(N=2)の  $g_m$ -C PPF を適用した場合の 6-bit 移相器の RMS 移相量誤差  $\phi_{rms}$  と RMS 振幅誤差  $A_{rms}$

## 3.2.2.5. gm-C PPF を適用した移相器の設計例

ここでは、前節までの議論から得られた VSPS における  $g_m$ -C PPF と VSPS の設計例について述べる。目標性能を表 3-1 に示す。

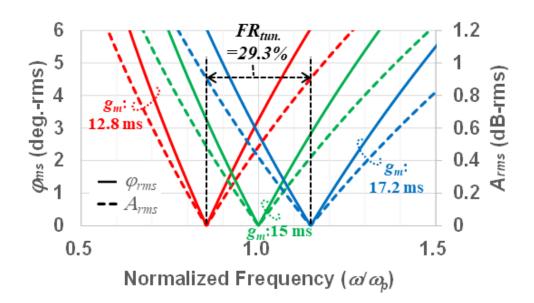

まず、必要となる比帯域を I/Q 誤差から決定する。振幅誤差は  $g_m$ -C PPF を用いることで自動的に満足するため、位相誤差のみに着目する。1 段、2 段を選択すると  $1^o$ -rms の移相量誤差と 0.15 dB-rms の振幅誤差が得られる比帯域が 9.7 %、もしくは 63.9 %と自動的に決定する。ここでは表 3-1 に示す目標性能より 1 段を選択する。容量 C とトランスコンダクタンス $g_m$ は中心角周波数 $\omega_p$ と周波数可変範囲から決定する。大きな容量を選んだ場合、より高い $g_m$ が必要となり、より大きな電流が必要となる。 $g_{m,1\_av\_max}$ は半導体プロセステクノロジーで選択可能な最大値が決まる。ここでは、容量値は 907 fF、 $g_{m,1\_min}$ は 12.8 mS、 $g_{m,1\_max}$ は 17.2 mS とした。続いて、負荷抵抗Rを電圧利得Gと利得変動幅 $\Delta G$ から (3-16)式と (3-23)式を用いて決定する。ここでは 300  $\Omega$ 以上の抵抗が必要となるため、472  $\Omega$ を選択する。電圧利得を利得変動幅 $\Delta G$  は 2.9 dB と 0.1 dB 以下となる。最後に $g_{m,n\_max}$ が $g_{m,n\_av\_max}$ より小さいことを確認する。 $V_{BE}$  = 0.7 V、VCC = 2 V、 $V_t$  = 26 mV、 $\alpha$  = 5 とすると、 $V_{CE} \ge V_{BE}$  とすると (3-22)式より  $g_{m,n\_av\_max}$ は 21.2 mS となる。 $g_{m,n\_max}$ は 17.2 mS のため 21 mS より小さいため本値で成り立つことがわかる。最大可変周波数範囲 $FR_{tun\_av\_max}$ は、(3-24)式、もしくは (3-25)式より 39.3%と計算される。表 3-2 に計算された定数一覧を示す。

図 3-7 に 1 段の gm-C PPF を適用した 6-bit 移相器における $g_m$ を変化させたときの RMS 移相量誤差計算結果を示す。ここで、 $g_{m,n}$ は(3-27)式を用いて 12.8 mS $\sim$ 17.2 mS で変化させている。角周波数は  $\omega_p=15$  ms/907 fF =  $16.5\times10^9$  rad/s(周波数に換算して2.63 GHz)で規格化している。 $FR_{tun}$ は 29.3%、TBWは(3-28)式より 29.3% + 9.7%=39.0%となる。

表 3-1 g<sub>m</sub>-C PPF の目標性能

| Parameters                                     | Value                   |  |  |  |  |  |

|------------------------------------------------|-------------------------|--|--|--|--|--|

| Gain                                           | >2.5 dB                 |  |  |  |  |  |

| Gain variation \( \Delta Gain \)               | <0.1 dB                 |  |  |  |  |  |

| Tunable frequency range FR <sub>tun.</sub>     | 2.25 -3.02 GHz (29.3 %) |  |  |  |  |  |

| Relative bandwidth of VSPS lower               | 9.7 %                   |  |  |  |  |  |

| than $1^{\circ}$ -rms and $0.15~\text{dB-rms}$ | 9.1 %                   |  |  |  |  |  |

| VCC                                            | 2.0 V                   |  |  |  |  |  |

表 3-2 計算された g<sub>m</sub>-C PPF の定数

| Devices        | Value    |  |  |  |  |  |

|----------------|----------|--|--|--|--|--|

| R              | 472 ohms |  |  |  |  |  |

| C              | 907 fF   |  |  |  |  |  |

| $g_{m,1\_max}$ | 17.2 mS  |  |  |  |  |  |

| $g_{m,1\_min}$ | 12.8 mS  |  |  |  |  |  |

図 3-7 1 段の  $g_m$ -C PPF を適用した 6-bit 移相器における  $g_m$  を変化させたときの RMS 移相量誤差計算結果

## 3.3. 試作結果

#### 3.3.1. 試作回路

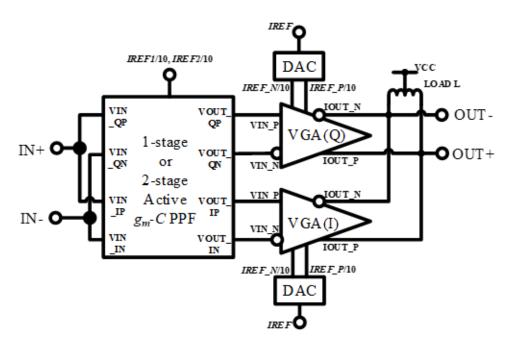

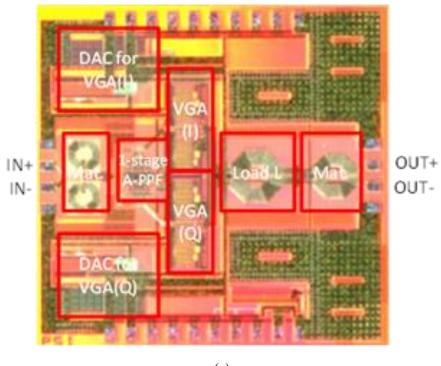

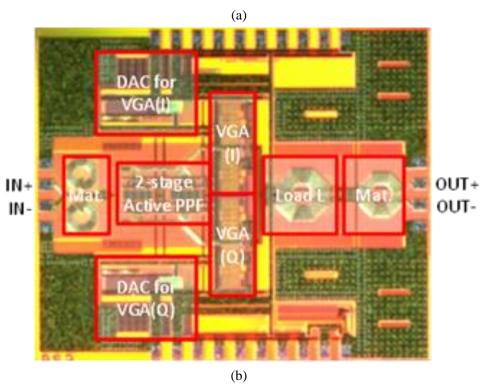

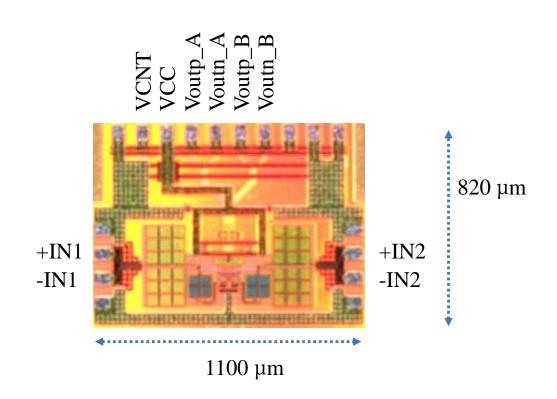

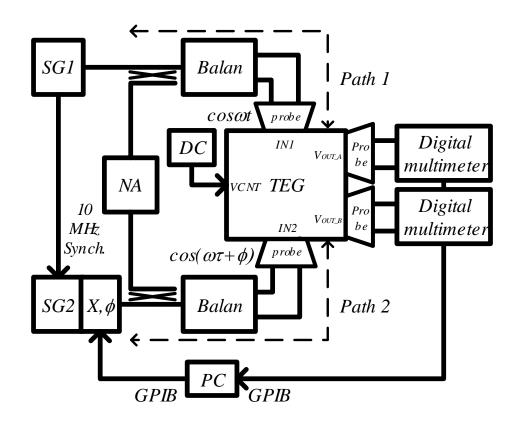

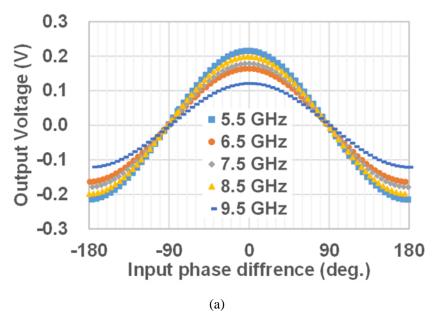

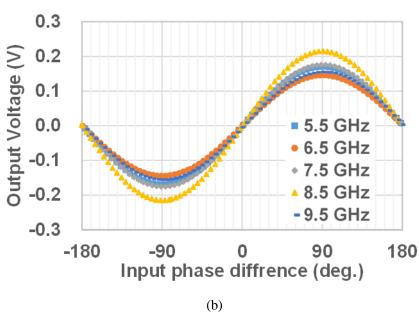

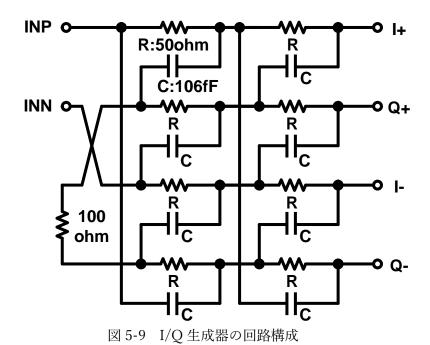

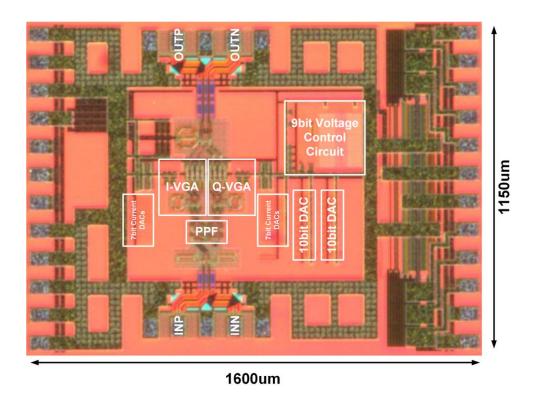

前章までに説明した 1 段、および 2 段の  $g_m$ -C を実装した VSPS の試作を実施した。VSPS の回路図を図 3-8 に示す。VSPS は  $g_m$ -C PPF、I/Q 経路の VGA(Q)、VGA(I)、および Digital Analog to Converter (DACs)からなる。入力信号は 1 段、もしくは 2 段の  $g_m$ -C PPF によって I/Q 信号に分配され、それぞれが I/Q の VGA によって振幅と極性が調整されたのちに合成されることで移相信号を得る。半導体プロセステクノロジーとして  $0.13~\mu m$  SiGe-BiCMOS を用いて試作した 1 段、および 2 段の  $g_m$ -C を伴う 6-bit VSPS のチップ写真を図 3-9 に示す。チップサイズは、整合回路(Mat.)や配線用パッドを含めそれぞれ  $1600~\mu m$  ×  $1500~\mu m$ 、 $1800~\mu m$  ×  $1500~\mu m$  である。1 段、2 段  $g_m$ -C PPF を伴う VSPS の電流は、電源電圧 2 V において 8.75~mA、11.26~mA である。内訳としては、 $g_m$ -C PPF 単段が 2.51~mA、単段 VGA が 2.90~mA、DAC が 0.22~mA となる。以下、各々の個別回路を説明する。

図 3-8 VSPS の回路図

図 3-9 6-bit VSPS チップ写真 (a)1 段  $g_m$ -C PPF、(b) 2 段  $g_m$ -C PPF

## 3.3.1.1. g<sub>m</sub>-C ポリフェーズフィルタ(PPF)

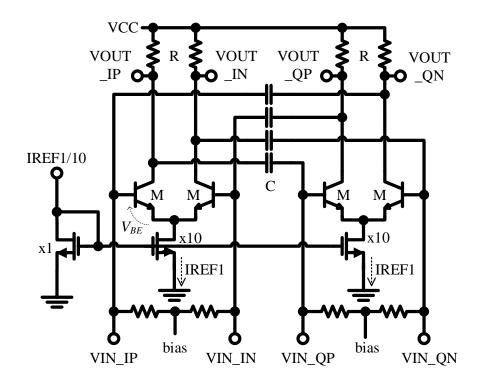

図 3-10 に 1 段  $g_m$ -C PPF の実際の回路図を示す。 $g_m$ -C PPF はテール電流を有する、4 つのトランジスタ M を用いた二つの差動対、4 つの負荷抵抗 R と 4 つの帰還容量 C、入力バイアス抵抗からなる。2 段  $g_m$ -C PPF の場合、入力バイアス抵抗は初段のみの搭載である。表 3-3 にデバイスパラメータを示す。本値は 3.2.2.5 節で求めた値と同じである。電流IREF1 の調整範囲は  $800~\mu$ A  $\sim$   $1200~\mu$ A であり、これはシミュレーションにて $g_m$ は 12.8~mS  $\sim$  17.2~mS に対応することを確認している。

図 3-10 1 段 g<sub>m</sub>-C PPF の実際の回路図

表 3-3 g<sub>m</sub>-C PPF のデバイスパラメータ

| Devices        | Parameters        |  |  |  |  |  |  |

|----------------|-------------------|--|--|--|--|--|--|

| M              | 0.13 μm / 3 μm    |  |  |  |  |  |  |

| С              | 907 fF            |  |  |  |  |  |  |

| R              | 472 ohms          |  |  |  |  |  |  |

| $g_{m,1\_max}$ | 17.2 mS (1200 μA) |  |  |  |  |  |  |

| $g_{m,1\_min}$ | 12.8 mS (800 μA)  |  |  |  |  |  |  |

| VCC            | 2 V               |  |  |  |  |  |  |

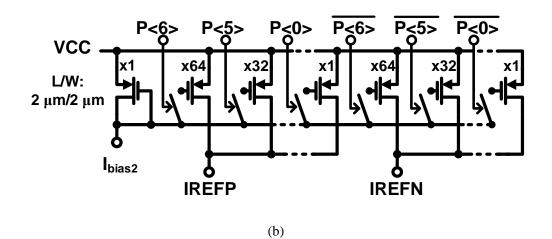

## 3.3.1.2. 可変利得增幅器(VGA)

図 3-11 に VGA の回路図を示す。VGA はテール電流 $IREF\_P$ と $IREF\_N$ を有する 2 つの差動対からなる。理想的な電圧利得は以下のように $IREF\_P$ と $IREF\_N$ の差分で与えられる。

$$\frac{\Delta Vout}{\Delta Vin} = \frac{Z(IREF\_P - IREF\_N)}{\alpha V_t}$$

(3-29)

ここで、 $V_t$ は熱電圧であり、 $\alpha$ は半導体のプロセステクノロジーによって決まる定数、Zは負荷インピーダンスである。シミュレーションにより VGA の利得は約 8 dB であり、 2 つの VGA を用いることでベクトル合成器として動作する[3.3]。デバイスパラメータを表 3-4 に示す。

図 3-11 VGA の回路図

表 3-4 VGA のパラメータ

| Devices | Parameters                  |

|---------|-----------------------------|

| M       | $0.13~\mu m \ / \ 10~\mu m$ |

| IREF_P  | 0  mA - 2.4  mA             |

| IREF_N  | 2.4 mA – 0 mA               |

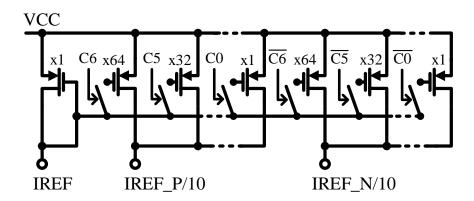

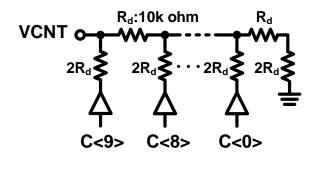

## 3.3.1.3. Digital to Analog Converter (DAC)

図 3-12 に DAC の回路図を示す。DAC はバイナリ型の 7-bit PMOS カレントミラーである。最小 PMOS のゲート幅 W /ゲート長 L は、それぞれ  $2\,\mu\text{m}/5\,\mu\text{m}$  である。

図 3-12 DAC 回路図

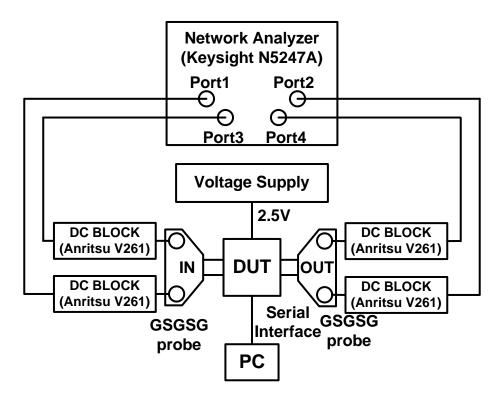

#### 3.3.2. 測定結果

ここでは 6-bit VSPS の測定結果を示す。1 段  $g_m$ -C PPF は $\omega_p$ の制御による移相量誤差の改善の検証を目的とし、2 段  $g_m$ -C PPF はより広い周波数帯域での低移相量誤差の実証を目的とした。本測定において、VGA(I)と VGA(Q)の制御値としては、理想値(VGA(I):  $\sin\theta$ 、 VGA(Q):  $\cos\theta$ )を用いた。IC の測定には GSSG プローブと 4 ポートのベクトルネットワークアナライザ(Keysight N5247A)を用いている。

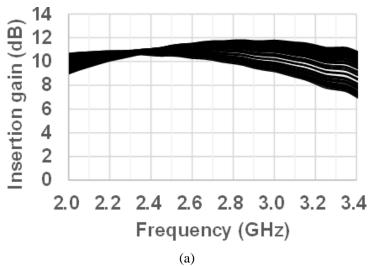

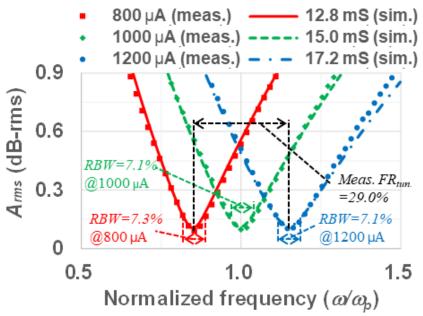

## 3.3.2.1. 1段 g<sub>m</sub>-C PPF を装荷した VSPS

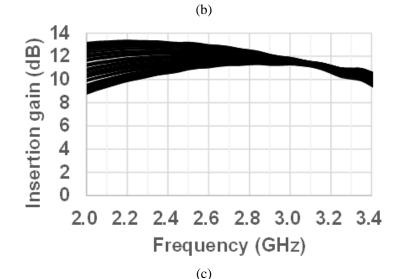

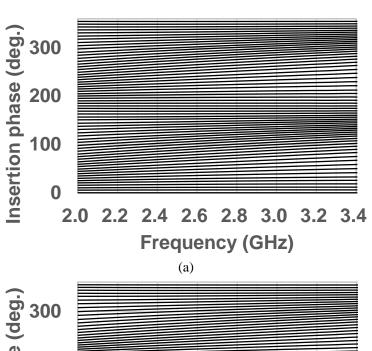

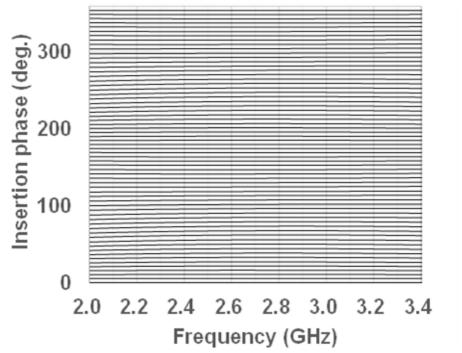

図 3-13 にIREF1を 800 µA、1000 µA、1200 µA で変化させたときの 360° 移相(5.625° ス テップ)時の通過利得を示す。それぞれのIREF1は、理想値としてトランスコンダクタンス $g_m$ の  $12.8\,\mathrm{mS}$ 、 $15\,\mathrm{mS}$ 、 $17.2\,\mathrm{mS}$  に対応し、 $f_p$ は  $2.25\,\mathrm{GHz}$ 、 $2.63\,\mathrm{GHz}$ 、 $3.02\,\mathrm{GHz}$  に対応する。 図 3-13 よりIREF1を変化させることで、通過利得の変動量が最小となる周波数が 2.34 GHz、 2.73 GHz、3.08 GHz と変化しており、 $\omega_{n,1}$ がIREF1の増加に対し線形に増加していることが わかる。理想値から数%のずれが見られ、本原因はプロセスばらつきによる容量値、または トランスコンダクタンスの絶対値ずれと推定される。図 3-14 にIREF1を変化させたときの 平均通過利得と利得ばらつきを示す。平均通過利得は 5.625° ステップで測定したすべての 通過利得の平均値である。周波数範囲 2.2~3.2 GHz において、10.7 dB という高い通過利得 と、0.4 dB 以下の平均利得ばらつきを確認した。図 3-15 にIREF1を 800 μA、1000 μA、1200 μA で変化させたときの 360° 移相(5.625° ステップ)時の通過位相を示す。図 3-16 と図 3-17 に図 3-13 と図 3-15 から計算した RMS 振幅誤差と RMS 移相量誤差のシミュレーション結 果と実測結果の比較を示す。周波数はIREF1=1000 μA の値で規格化している。図 3-16 と図 3-17 よりIREF1を変化させることで $\omega_n$ が変化し、RMS 振幅誤差、RMS 移相量誤差ともに $\omega_n$ で最小となる結果が得られ、また、シミュレーション結果と実測結果はよく一致することを 確認した。*FR<sub>tun.</sub>の*実測値は 29.0%であり、本値は 3.2.2.5 節で求めた 29.3%よく一致するこ とを確認した。RMS 振幅誤差 0.15 dB-rms 以下となる比帯域は 7.3%@800 µA、7.1%@1000 μΑ、7.1%@1200 μΑ であり、RMS 移相量誤差が 1°-rms 以下となる比帯域は 10.6%@800 μΑ、 10.0%@1000 μA、10.4%@1200 μA と章で求めた 9.7%とほぼ同等の値が得られることを確 認した。TBWの実測値は 29.0%+10.0%=39.0%となり、3.2.2.5 節で求めた計算値 39.0%と 一致した。振幅誤差 0.12 dB-rms と移相量誤差が 0.38°-rms 以下となる比帯域は 100 MHz 以上である。

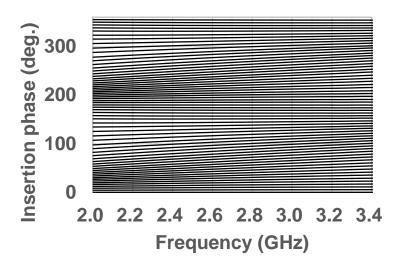

図 3-13 360°移相(5.625°ステップ)時の通過利得 (a) IREF1=800  $\mu$ A (b) IREF1=1000  $\mu$ A (c) IREF1=1200  $\mu$ A

図 3-14 IREF1 を変化させたときの平均通過利得と利得ばらつき

図 3-15 360°移相(5.625°ステップ)時の通過位相

(a) IREF1=800 μA (b) IREF1=1000 μA (c) IREF1=1200 μA.

(c)

図 3-16 RMS 振幅誤差のシミュレーション結果と実測結果の比較

図 3-17 RMS 移相量誤差のシミュレーション結果と実測結果の比較

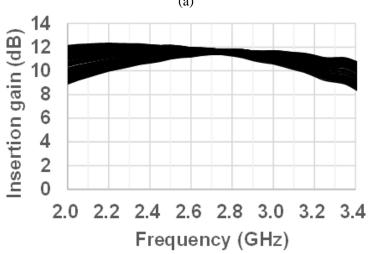

#### 3.3.2.2. 2 段 g<sub>m</sub>-C PPF を装荷した VSPS

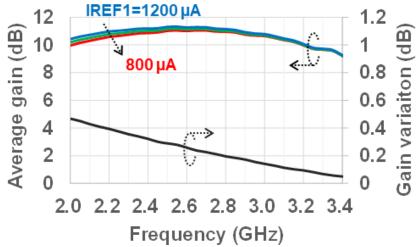

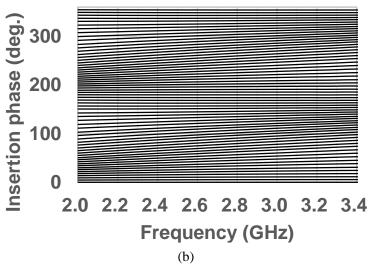

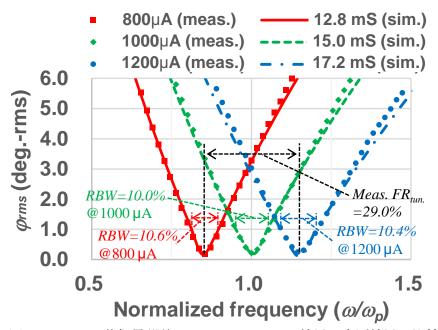

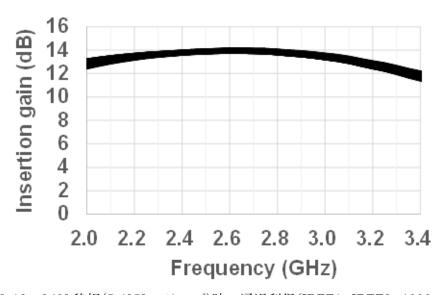

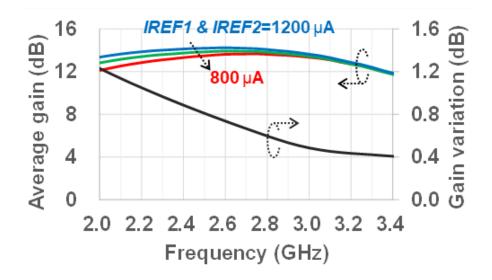

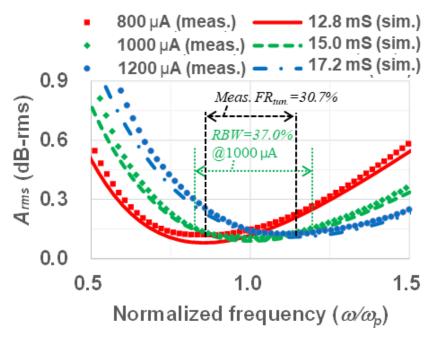

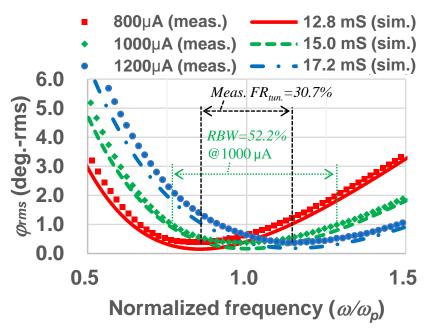

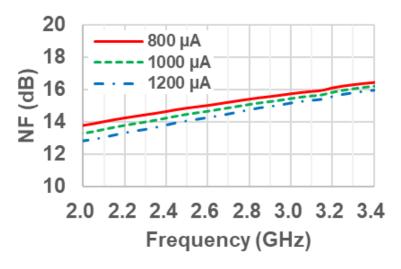

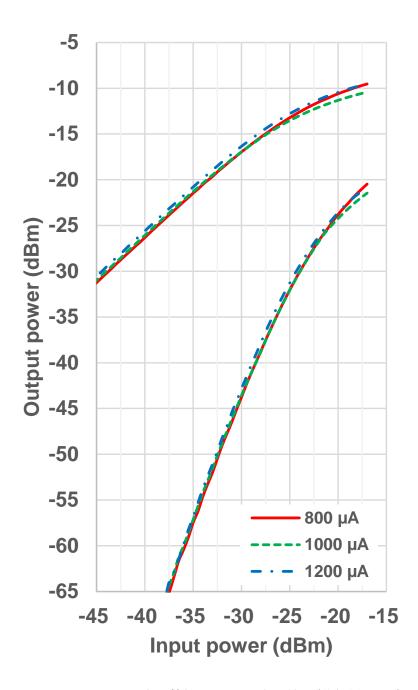

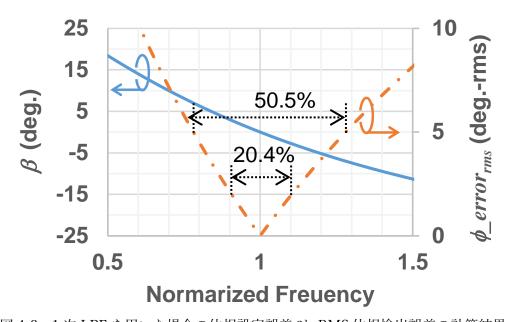

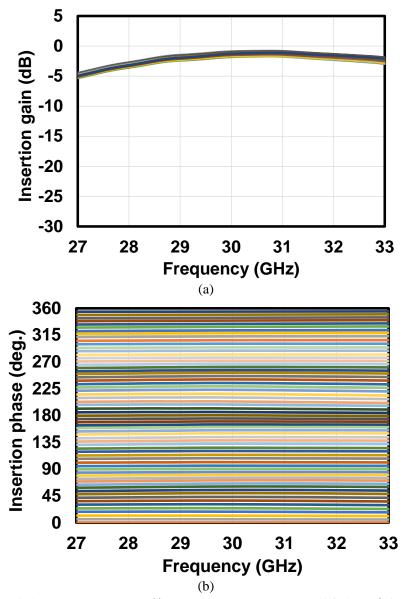

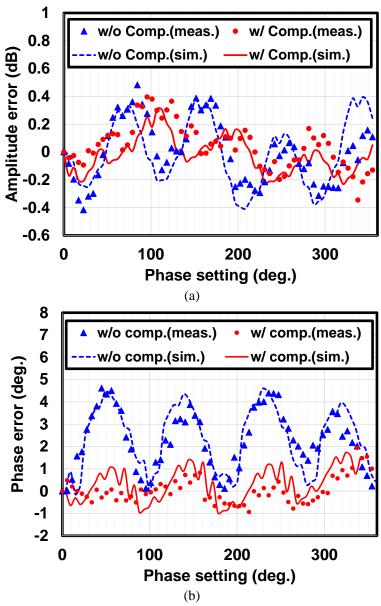

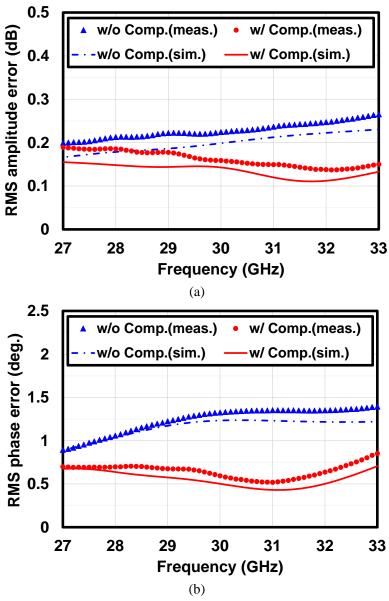

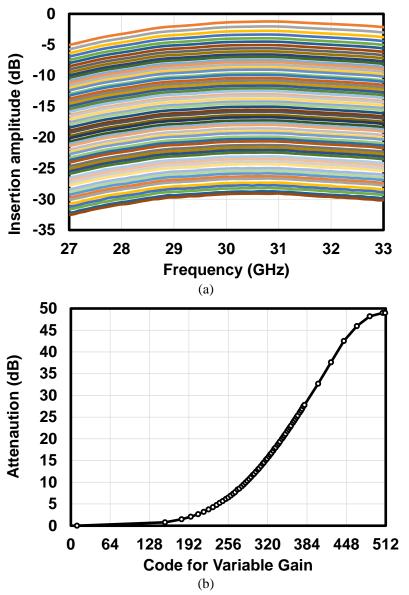

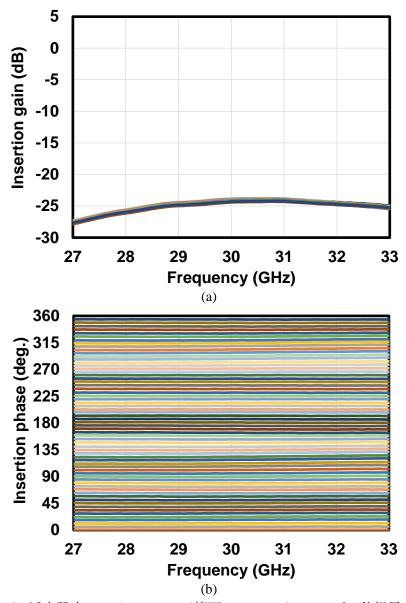

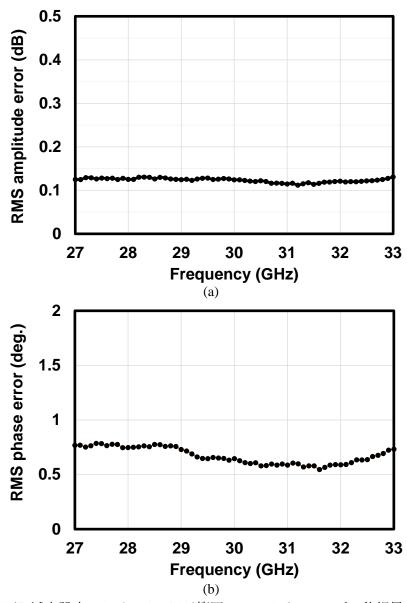

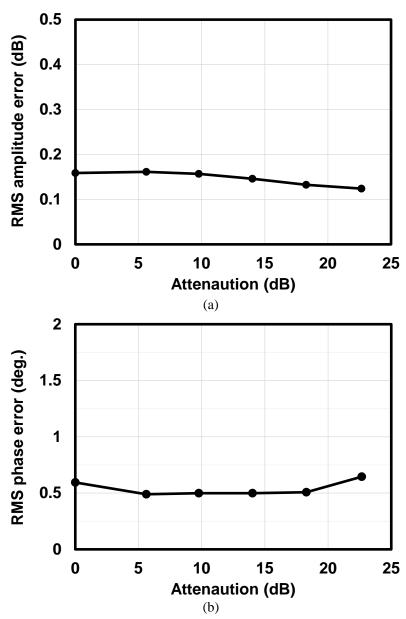

より広帯域での低振幅誤差、低移相量誤差を 2 段 gm-C PPF を装荷した VSPS で実現で きることを確認する。本測定では、1 段目と 2 段目の g<sub>m</sub>-C PPF の電流*IREF*1、*IREF*2の双 方とも同じ値(800 μA/1000 μA/1200 μA)を用いた。図 3-18、図 3-19 に 360° 移相(5.625° ス テップ)時の通過利得と通過位相(IREF1= IREF2=1000 μA)を示す。図 3-20 にIREF1と IREF2を同時に  $800 \,\mu\text{A}/1000 \,\mu\text{A}/1200 \,\mu\text{A}$  で変化させたときの平均利得と利得ばらつき $\Delta G$ を 示す。周波数範囲 2.2 GHz~3.2 GHz において、13.4 dB の平均通過利得と、1.0 dB の利得 ばらつきを確認した。 2 段にすることでおおよそ 3.0 dB の高利得化が得られることを確認し た。図 3-21、図 3-22 に RMS 振幅誤差と RMS 移相量誤差のシミュレーション結果と実測 結果の比較を示す。シミュレーション結果と実測結果はよく一致していることを確認する とともに、RMS 振幅誤差 0.15 dB-rms 以下となる比帯域は 37.0%、RMS 移相量誤差が 1ºrms 以下となる比帯域が 52.2%と 1 段と比較し広い比帯域が得られることを確認した。これ により、多段化による広帯域化をたやすく実現できることを確認した。振幅誤差 0.13 dB-rms と移相量誤差が 0.52°-rms 以下となる比帯域は 500 MHz 以上である。図 3-23 に NF(Noise figure)の実測結果を示す。また、図 3-24 に入出力特性と IM3(Inter Modulation 3rd)の実測 結果を示す。ここで、移相量は  $45^{\circ}$ とした。 $\omega_{p}$ の制御に起因する NF や IM3 の変化は  $1.0\,\mathrm{dB}$ 以下であり、影響は軽微であることを確認した。

図 3-18 360° 移相(5.625° ステップ)時の通過利得(IREF1=IREF2=1000 μA)

図 3-19 360° 移相(5.625° ステップ)時の通過位相(IREF1=IREF2=1000 μA)

図 3-20 IREF1 & IREF2 を変化させたときの平均通過利得と利得ばらつき

図 3-21 RMS 振幅誤差のシミュレーション結果と実測結果の比較

図 3-22 RMS 移相量誤差のシミュレーション結果と実測結果の比較

図 3-23 NF 実測結果

図 3-24 入出力特性と IM3 の実測結果(移相量: 45°)

#### 3.4. むすび

本章では、AESA の広帯域化をメインターゲットとし、広帯域に低移相量誤差な移相技術 を実現するため、ベクトル合成型移相器において一般的に用いられる抵抗と容量で構成さ れる I/Q 生成器の抵抗をトランジスタに置き換えた gm-C PPF を用いた移相器を提案した。 提案した回路において、従来の I/Q 生成器の一つである RC-PPF と等価な周波数特性が得ら れるとともに、RC-PPF では不可能であった正の通過利得を実現する条件と、@。の制御によ る I/Q バランスの周波数調整範囲を解析的に示し、広帯域に低移相誤差な VSPS を実現する ための設計法を明らかにした。この設計法に基づいた gm-C PPF を実装した C 帯の VSPS を 試作し、2.2~3.3 GHz という周波数帯域において 1°以下の低移相量誤差、また、22.6 mW 程 度の低消費電力で 13.4 dB 以上の高利得が実現可能なことを実証した。表 3-5 に他文献との 比較を示す。提案した移相器は、チップ外部の回路を用いない他文献と比較し、最も高い周 波数帯域/RMS 移相量誤差の値を示しており、広帯域な低移相量誤差を実証した。また、他 文献と比較しほぼ同等の消費電力でより高い通過利得を実現するとともに、同等の雑音指数 が実現できているため、本回路構成は受信機などのより低雑音性能が求められるアプリケー ションに適していると考えられる。回路規模と消費電力の観点からは、提案手法は I/Q 生成 器にて利得を得ることができるため、従来方式において必要であった通過損失を補償する追 加の増幅器を削減でき、回路の小型化と低消費電力化にも有用であると考えられる。以上よ り、提案する gm-C PPF が従来の I/Q 生成器の課題であった損失量と比帯域幅のトレードオフ を解消し広帯域に低移相量誤差性能を実現できるとともに、g<sub>m</sub>-C PPF を適用した移相器の回 路構成とその設計法が AESA の広帯域化とビーム制御高精度化への有用性を示すものであ ると言える。

表 3-5 移相器の性能についての他文献との比較

| プ 消費<br>ズ 電力<br>引 (mW)                | 17.5                                     | ) 22.6                                  | 1 27.5                  | *2 28.0         | 9 20.3          | *2 95.4         | 54.0              | *2 28.0                 | 1.61            | ¥2 24.0              | 61.7 *4                      | *2 90.0               | *2 133.0              | 4 93.1                  |

|---------------------------------------|------------------------------------------|-----------------------------------------|-------------------------|-----------------|-----------------|-----------------|-------------------|-------------------------|-----------------|----------------------|------------------------------|-----------------------|-----------------------|-------------------------|

| + チップ<br>サイズ<br>(mm²)                 | 2.40                                     | 2.70                                    | 1.21                    | 0.30 *2         | 0.89            | 6.04 *2         | 2.0               | 1.08 *2                 | 0.84            | 0.38*2               | 06:0                         | 0.72 *2               | 0.64 *2               | 2.44                    |

| I/Q生成器<br>面積<br>(mm²)                 | 0.054                                    | 0.108                                   | -                       | 0.066 *3        | ,               | '               | 0.063 *3          | -                       | 0.471 *3        |                      | 0.044 *3                     | -                     | 1                     | 0.152 *3                |

| 製造半導体プロセス                             | 0.13-µm                                  | SiGeBiCMOS                              | 0.13-μm<br>CMOS         | 0.13-μm<br>CMOS | 0.13-μm<br>CMOS | 0.18-μm<br>CMOS | 0.13-μm<br>CMOS   | 0.13-μm<br>CMOS         | 0.18-µm<br>CMOS | 0.18-μm<br>CMOS      | 0.18-µm<br>SiGeBiCMOS        | 0.25-µm<br>SiGeBiCMOS | 0.18-μm<br>SiGeBiCMOS | 0.13-µm<br>SiGeBiCMOS   |

| 維音指数<br>(dB)                          | 14.0±1.4                                 | 14.1±2.1                                | 12±1                    | ı               | ı               | ı               | ı                 | -                       | 1               | 13.0±2               | 4.9±0.8<br>@7.5-15.2GHz *4   | ı                     | ı                     | ı                       |

| IP1dB<br>(dBm)                        | -25.5                                    | -25.8                                   | -19.5±2.5               | -12.9±1         | 1               | 4               | 4±1               | 5.7±1.1                 | 1.8±1.2         | -13.5                | -36.5 *4                     | 3.5                   | 18.5±7.5              | 5-8                     |

| 周波数比带域/<br>RMS移相量誤差<br>(%/degree-rms) | 5.79                                     | 71.2                                    | 24.2                    | 1.9             | 15.6            | 8.2             | 51.8              | 107.3                   | 50.3            | 8.0                  | 17.9                         | 11.3                  | 36.3                  | 17.9                    |

| RMS移相量誤差<br>(degree-ms)               | <1.0 (RBW:10.0%)<br><0.38(RBW:100 MHz)   | < 1.0 (RBW:52.2%)<br><0.52(RBW:500 MHz) | 4                       | 1.25-9.7        | <7.2            | <4.5            | <2.5              | <1.8                    | <1.4            | \$                   | >5.6                         | 6.7>                  | <2.1                  | <5.6                    |

| RMS振幅誤差<br>(dB-ms)                    | < 0.15 (RBW:7.1%)<br>< 0.12(RBW:100 MHz) | <0.15 (RBW:37.0%)<br><0.13(RBW:500 MHz) | <0.95                   | 0.5-0.7         | <0.74           |                 | <0.17             | <0.27                   | <1.1            | <1.2                 | <                            | <2.2                  | <0.5                  | <1.05                   |

| 通過利得<br>(dB)                          | 10.7±0.7                                 | 13.4±0.9                                | 9±1                     | -0.1±1.15       | 3.52            | -8.75±3.75      | 5.25±0.75         | 3                       | -1.2±1          | 1.5±1.5              | 18±1.5<br>@7.5-15.2GHz<br>*4 | -7.8                  | -11±1.5               | 1.6±1.4<br>@7.5-15.2GHz |

| 周波数<br>(GHz)                          | 2.2-3.2                                  | 2.2-3.2                                 | 0.5-6                   | 4.9-5.9         | 0.75-2.67       | 2.2-3.2         | 0.6-2.8           | 0.1-5.7                 | 2.3-4.8         | 2-3                  | 6-18                         | 5-13                  | 6.5-14.5              | 6-18                    |

| I/Q生成器<br>方式                          | 1-stage<br>g <sub>m</sub> -C PPF         | 2-stage<br>g <sub>m</sub> -C PPF        | 90 degree<br>hybrid * 1 | RLC-QAF         | RC-QAF          | RLC-QAF         | 3-stage<br>RC-PPF | 90 degree<br>hybrid * 1 | RLC-QAF         | OTA &<br>Capasitance | RLC-QAF                      | 2-stage<br>RC-PPF     | 2-stage<br>RC-PPF     | RLC-QAF                 |

|                                       | This work1                               | This work2                              | [3.6]                   | [3.7]           | [3.8]           | [3.9]           | [3.10]            | [3.11]                  | [3.12]          | [3.20]               | [3.22]                       | [3.23]                | [3.24]                | [3.25]                  |

\*1 offchip, \*2 excluding the pads, \*3 estimation from chip photographs \*4 including an input amplifier

## 3.5. 参考文献

- [3.1] I. Kalyoncu, E. Ozeren, A. Burak, O. Ceylan and Y. Gurbuz, "A Phase-Calibration Method for Vector-Sum Phase Shifters Using a Self-Generated LUT," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 4, pp. 1632-1642, April 2019, doi: 10.1109/TCSI.2018.2885172.

- [3.2] J. Pang et al., "A 28-GHz CMOS Phased-Array Transceiver Based on LO Phase-Shifting Architecture With Gain Invariant Phase Tuning for 5G New Radio," in IEEE Journal of Solid-State Circuits, vol. 54, no. 5, pp. 1228-1242, May 2019, doi: 10.1109/JSSC.2019.2899734.

- [3.3] I. Kalyoncu, A. Burak, M. Kaynak and Y. Gurbuz, "A 26-GHz Vector Modulator in 130-nm SiGe BiCMOS Achieving Monotonic 10-b Phase Resolution Without Calibration," 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019, pp. 75-78, doi: 10.1109/RFIC.2019.8701733.

- [3.4] Y. Wang et al., "A 39GHz 64-Element Phased-Array CMOS Transceiver with Built-in Calibration for Large-Array 5G NR," 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019, pp. 279-282, doi: 10.1109/RFIC.2019.8701856.

- [3.5] B. Sadhu et al., "A 28-GHz 32-Element TRX Phased-Array IC With Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications," in IEEE Journal of Solid-State Circuits, vol. 52, no. 12, pp. 3373-3391, Dec. 2017, doi: 10.1109/JSSC.2017.2766211.

- [3.6] Hu Zijie and K. Mouthaan, "A 0.5–6 GHz 360° vector-sum phase shifter in 0.13-μm CMOS," 2014 IEEE MTT-S International Microwave Symposium (IMS2014), Tampa, FL, USA, 2014, pp. 1-3, doi: 10.1109/MWSYM.2014.6848604.

- [3.7] M. -M. Mohsenpour and C. E. Saavedra, "Variable 360° Vector-Sum Phase Shifter With Coarse and Fine Vector Scaling," in IEEE Transactions on Microwave Theory and Techniques, vol. 64, no. 7, pp. 2113-2120, July 2016, doi: 10.1109/TMTT.2016.2574843.

- [3.8] T. -C. Yan, W. -Z. Lin and C. -N. Kuo, "A 0.75–2.67 GHz 5-bit vector-sum phase shifter," 2013 European Microwave Integrated Circuit Conference, Nuremberg, Germany, 2013, pp. 196-199.

- [3.9] E. V. Balashov and I. A. Rumyancev, "A fully integrated 6-bit vector-sum phase shifter in 0.18 um CMOS," 2015 International Siberian Conference on Control and Communications (SIBCON), Omsk, Russia, 2015, pp. 1-5, doi: 10.1109/SIBCON.2015.7146991.

- [3.10] Y. Xu, J. Xia and S. Boumaiza, "A 0.6–2.8GHz CMOS RF vector multiplier with low RMS magnitude and phase errors and high P1dB," 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 2017, pp. 2015-2017, doi: 10.1109/MWSYM.2017.8059062

- [3.11] J. Xia, Y. Xu, H. Huang and S. Boumaiza, "A 0.1-5.7 GHz CMOS Phase Shifter with 0.27dB/1.8° RMS Magnitude /Phase Errors and Enhanced Linearity," 2019 IEEE 19th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Orlando, FL, USA, 2019, pp. 1-3, doi: 10.1109/SIRF.2019.8709089.

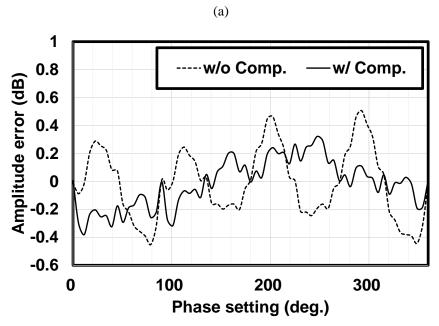

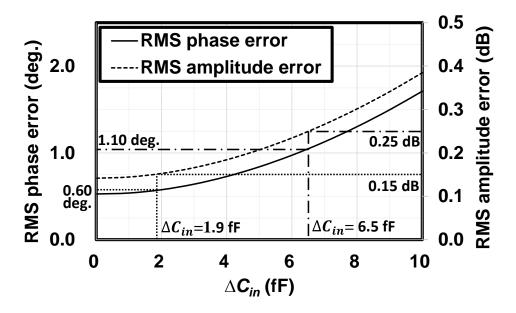

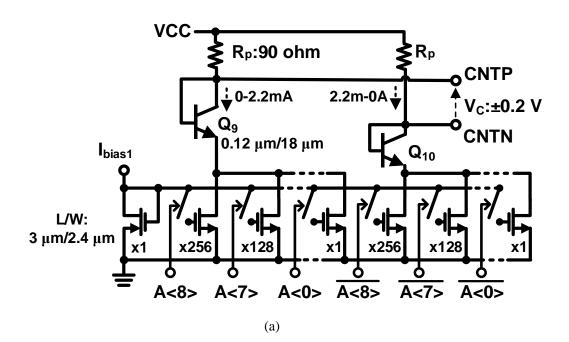

- [3.12] A. Asoodeh and M. Atarodi, "A Full 360° Vector-Sum Phase Shifter With Very Low RMS Phase Error Over a Wide Bandwidth," in IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 6, pp. 1626-1634, June 2012, doi: 10.1109/TMTT.2012.2189227.